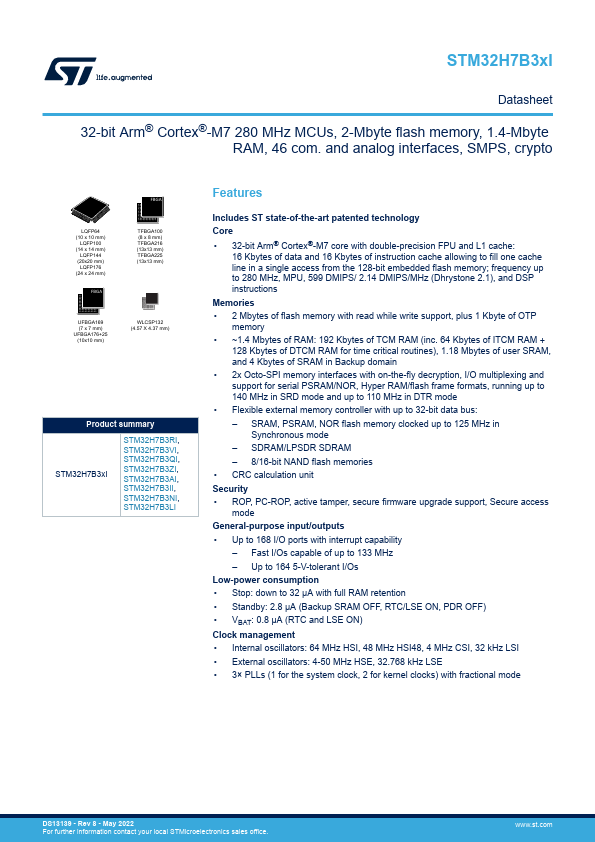

STM32H7B3LI

Overview

- 32-bit Arm® Cortex®-M7 core with double-precision FPU and L1 cache: 16 Kbytes of data and 16 Kbytes of instruction cache allowing to fill one cache line in a single access from the 128-bit embedded flash memory; frequency up to 280 MHz, MPU, 599 DMIPS/ 2.14 DMIPS/MHz (Dhrystone 2.1), and DSP instructions Memories

- 2 Mbytes of flash memory with read while write support, plus 1 Kbyte of OTP memory

- ~1.4 Mbytes of RAM: 192 Kbytes of TCM RAM (inc. 64 Kbytes of ITCM RAM + 128 Kbytes of DTCM RAM for time critical routines), 1.18 Mbytes of user SRAM, and 4 Kbytes of SRAM in Backup domain

- 2x Octo-SPI memory interfaces with on-the-fly decryption, I/O multiplexing and support for serial PSRAM/NOR, Hyper RAM/flash frame formats, running up to 140 MHz in SRD mode and up to 110 MHz in DTR mode

- Flexible external memory controller with up to 32-bit data bus: - SRAM, PSRAM, NOR flash memory clocked up to 125 MHz in Synchronous mode - SDRAM/LPSDR SDRAM - 8/16-bit NAND flash memories

- CRC calculation unit Security

- ROP, PC-ROP, active tamper, secure firmware upgrade support, Secure access mode General-purpose input/outputs

- Up to 168 I/O ports with interrupt capability - Fast I/Os capable of up to 133 MHz - Up to 164 5-V-tolerant I/Os Low-power consumption

- Stop: down to 32 µA with full RAM retention

- Standby: 2.8 µA (Backup SRAM OFF, RTC/LSE ON, PDR OFF)