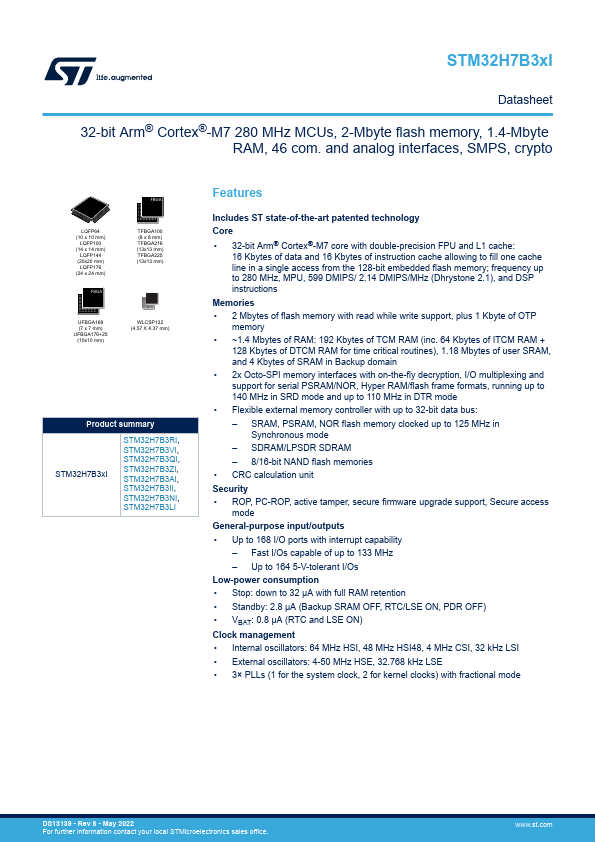

STM32H7B3QI Overview

Key Features

- 2 Mbytes of flash memory with read while write support, plus 1 Kbyte of OTP memory

- CRC calculation unit Security

- ROP, PC-ROP, active tamper, secure firmware upgrade support, Secure access mode General-purpose input/outputs

- Up to 168 I/O ports with interrupt capability – Fast I/Os capable of up to 133 MHz – Up to 164 5-V-tolerant I/Os Low-power consumption

- Stop: down to 32 µA with full RAM retention

- Standby: 2.8 µA (Backup SRAM OFF, RTC/LSE ON, PDR OFF)

- VBAT: 0.8 µA (RTC and L