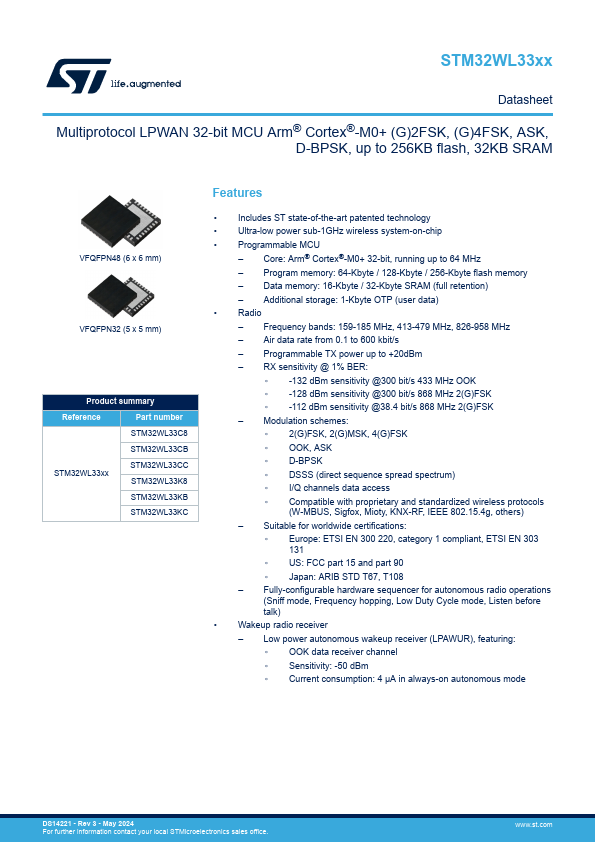

STM32WL33C8

Key Features

- Includes ST state-of-the-art patented technology

- Ultra-low power sub-1GHz wireless system-on-chip

- Programmable MCU - Core: Arm® Cortex®-M0+ 32-bit, running up to 64 MHz - Program memory: 64-Kbyte / 128-Kbyte / 256-Kbyte flash memory - Data memory: 16-Kbyte / 32-Kbyte SRAM (full retention) - Additional storage: 1-Kbyte OTP (user data)

- Radio - Frequency bands: 159-185 MHz, 413-479 MHz, 826-958 MHz - Air data rate from 0.1 to 600 kbit/s - Programmable TX power up to +20dBm - RX sensitivity @ 1% BER: ◦ -132 dBm sensitivity @300 bit/s 433 MHz OOK ◦ -128 dBm sensitivity @300 bit/s 868 MHz 2(G)FSK ◦ -112 dBm sensitivity @38.4 bit/s 868 MHz 2(G)FSK - Modulation schemes: ◦ 2(G)FSK, 2(G)MSK, 4(G)FSK ◦ OOK, ASK ◦ D-BPSK ◦ DSSS (direct sequence spread spectrum) ◦ I/Q channels data access ◦ Compatible with proprietary and standardized wireless protocols (W-MBUS, Sigfox, Mioty, KNX-RF, IEEE 802.15.4g, others) - Suitable for worldwide certifications: ◦ Europe: ETSI EN 300 220, category 1 compliant, ETSI EN 303 131 ◦ US: FCC part 15 and part 90 ◦ Japan: ARIB STD T67, T108 - Fully-configurable hardware sequencer for autonomous radio operations (Sniff mode, Frequency hopping, Low Duty Cycle mode, Listen before talk)

- Wakeup radio receiver - Low power autonomous wakeup receiver (LPAWUR), featuring: ◦ OOK data receiver channel ◦ Sensitivity: -50 dBm ◦ Current consumption: 4 µA in always-on autonomous mode