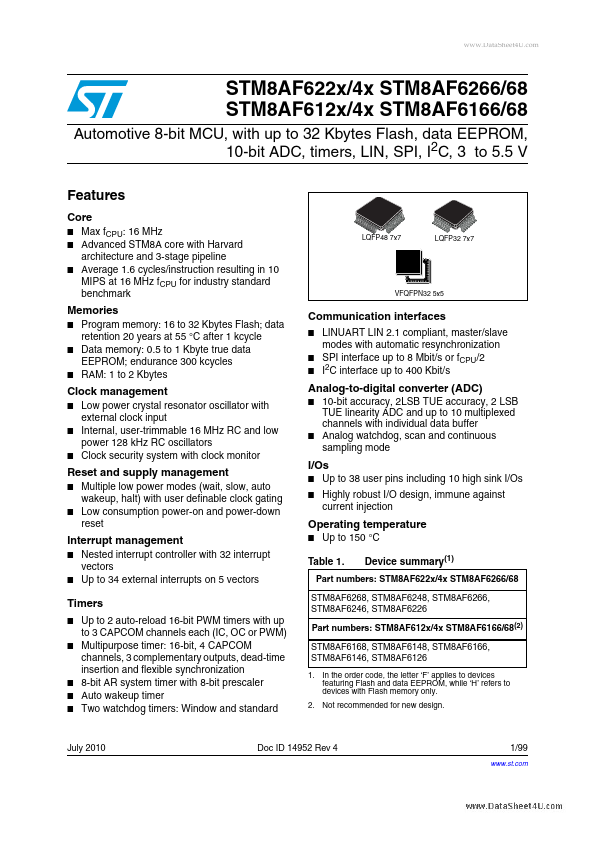

STM8AF6126

Overview

- Max fCPU: 16 MHz

- Advanced STM8A core with Harvard architecture and 3-stage pipeline

- Average 1.6 cycles/instruction resulting in 10 MIPS at 16 MHz fCPU for industry standard benchmark Memories

- Program memory: 16 to 32 Kbytes Flash; data retention 20 years at 55 °C after 1 kcycle

- Data memory: 0.5 to 1 Kbyte true data EEPROM; endurance 300 kcycles

- RAM: 1 to 2 Kbytes Clock management

- Low power crystal resonator oscillator with external clock input

- Internal, user-trimmable 16 MHz RC and low power 128 kHz RC oscillators

- Clock security system with clock monitor Reset and supply management

- Multiple low power modes (wait, slow, auto wakeup, halt) with user definable clock gating