Datasheet Summary

..

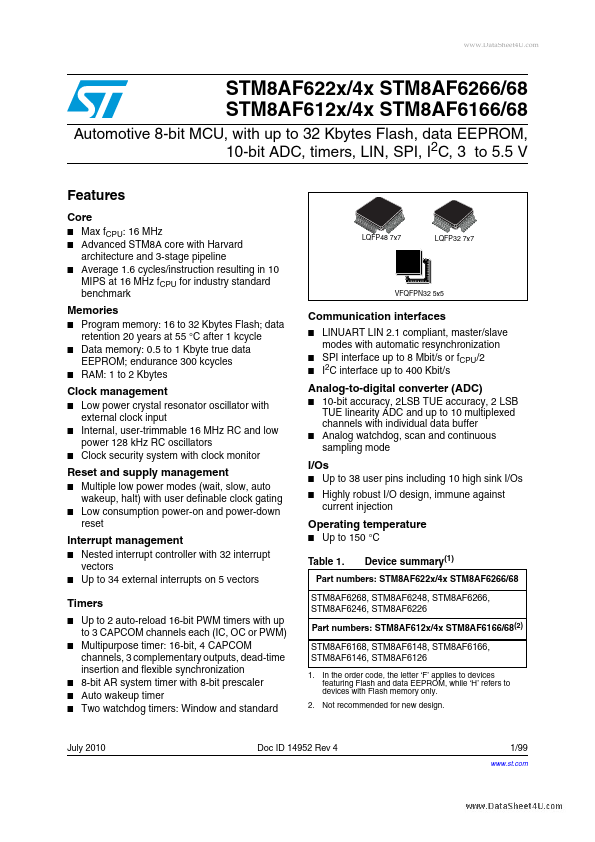

STM8AF622x/4x STM8AF6266/68 STM8AF612x/4x STM8AF6166/68

Automotive 8-bit MCU, with up to 32 Kbytes Flash, data EEPROM, 10-bit ADC, timers, LIN, SPI, I2C, 3 to 5.5 V

Features

Core

- Max fCPU: 16 MHz

- Advanced STM8A core with Harvard architecture and 3-stage pipeline

- Average 1.6 cycles/instruction resulting in 10 MIPS at 16 MHz fCPU for industry standard benchmark

LQFP48 7x7

LQFP32 7x7

VFQFPN32 5x5

Memories

- Program memory: 16 to 32 Kbytes Flash; data retention 20 years at 55 °C after 1 kcycle

- Data memory: 0.5 to 1 Kbyte true data EEPROM; endurance 300 kcycles

- RAM: 1 to 2 Kbytes munication interfaces

- LINUART LIN 2.1 pliant, master/slave modes with...