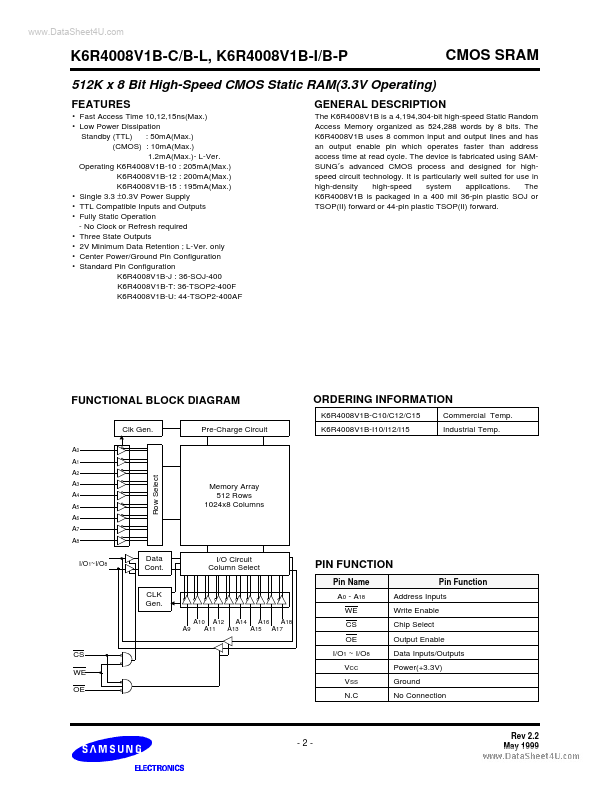

K6R4008V1B Description

The K6R4008V1B is a 4,194,304-bit high-speed Static Random Access Memory organized as 524,288 words by 8 bits. The K6R4008V1B uses 8 mon input and output lines and has an output enable pin which operates faster than address access time at read cycle. The device is fabricated using SAMSUNG′s advanced CMOS process and designed for highspeed circuit technology.

K6R4008V1B Key Features

- Fast Access Time 10,12,15ns(Max.)

- Single 3.3 ±0.3V Power Supply

- TTL patible Inputs and Outputs

- Fully Static Operation

- No Clock or Refresh required

- Three State Outputs

- 2V Minimum Data Retention ; L-Ver. only

- Center Power/Ground