KS88C01004 Description

KS88C01016/C01008/C01004/C01116/C01108/C01104 PRODUCT OVERVIEW 1 OVERVIEW .. PRODUCT OVERVIEW Samsung's KS88 series of 8-bit single-chip CMOS microcontrollers offers a fast and efficient CPU, a wide range of integrated peripherals, and various mask-programmable ROM sizes.

KS88C01004 Key Features

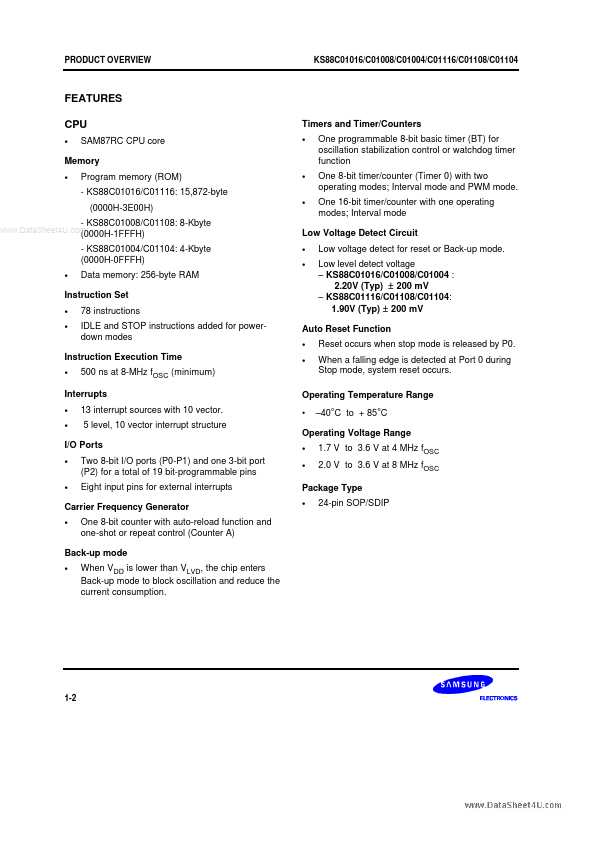

- Efficient register-oriented architecture

- Selectable CPU clock sources

- Idle and Stop power-down mode release by interrupt

- Built-in basic timer with watchdog function A sophisticated interrupt structure recognizes up to eight interrupt levels.

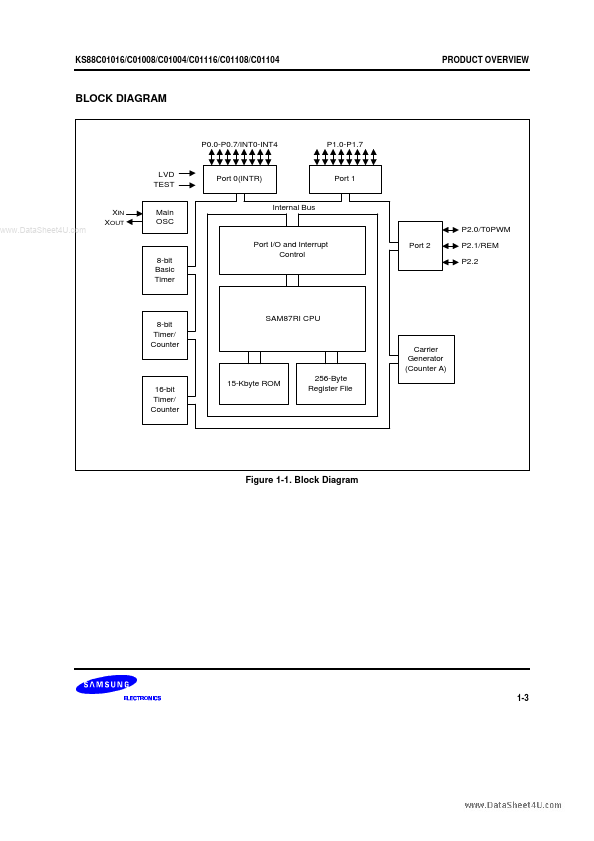

- Three programmable I/O ports, including two 8-bit ports and one 3-bit port, for a total of 19 pins

- Internal LVD circuit and eight bit-programmable pins for external interrupts

- One 8-bit basic timer for oscillation stabilization and watchdog functions (system reset)

- One 8-bit timer/counter and one 16-bit timer/counter with selectable operating modes

- Timers and Timer/Counters

- SAM87RC CPU core