ACS8525A

Key Features

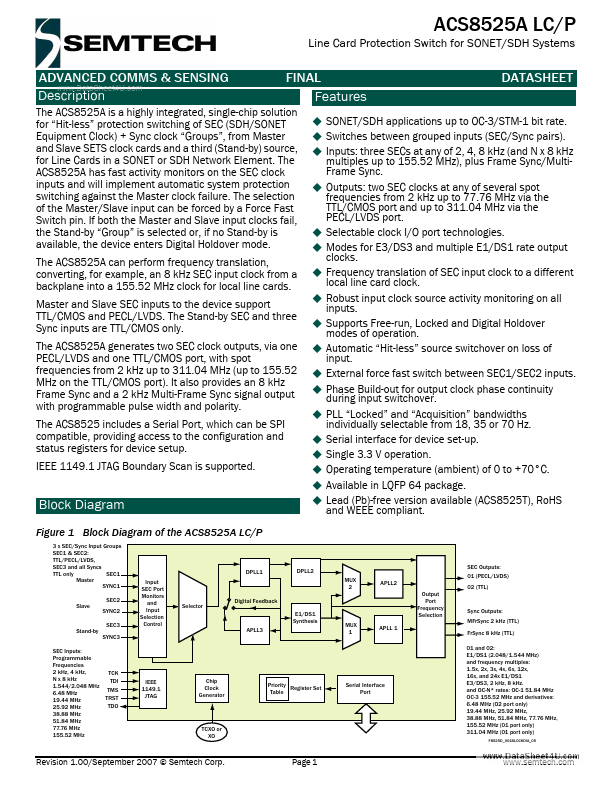

- The selection of the Master/Slave input can be forced by a Force Fast Switch pin

- Master and Slave SEC inputs to the device support TTL/CMOS and PECL/LVDS

- The Stand-by SEC and three Sync inputs are TTL/CMOS only

- It also provides an 8 kHz Frame Sync and a 2 kHz Multi-Frame Sync signal output with programmable pulse width and polarity

- The ACS8525 includes a Serial Port, which can be SPI compatible, providing access to the configuration and status registers for device setup

- IEEE 1149.1 JTAG Boundary Scan is supported