SK100E016

Key Features

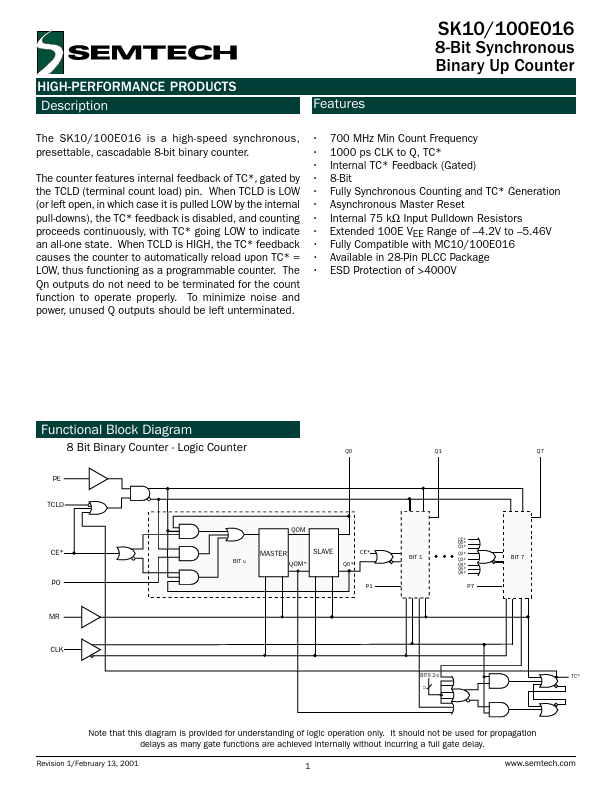

- 700 MHz Min Count Frequency 1000 ps CLK to Q, TC* Internal TC* Feedback (Gated) 8-Bit Fully Synchronous Counting and TC* Generation Asynchronous Master Reset Internal 75 kΩ Input Pulldown Resistors Extended 100E VEE Range of -4.2V to -5.46V Fully Compatible with MC10/100E016 Available in 28-Pin PLCC Package ESD Protection of >4000V .unctional Block Diagram 8 Bit Binary Counter - Logic Counter PE Q0 Q1 Q7 TCLD QOM CE* BIT 0 MASTER QOM* SLAVE Q0* CE* BIT 1 CE* Q0* Q1* Q2* Q3* Q4* Q5* Q6* BIT 7 PO P1 P7 MR CLK BITS 2-6 5 TC* Note that this diagram is provided for understanding of logic operation only. It should not be used for propagation delays as many gate functions are achieved internally without incurring a full gate delay. Revision 1/.ebruary 13, 2001 1