LH5496

Overview

- Fast Access Times: 15 */20/25/35/50/65/80 ns

- Full CMOS Dual Port Memory Array

- Fully Asynchronous Read and Write

- Expandable-in Width and Depth

- Full, Half-Full, and Empty Status Flags

- Read Retransmit Capability

- TTL Compatible I/O

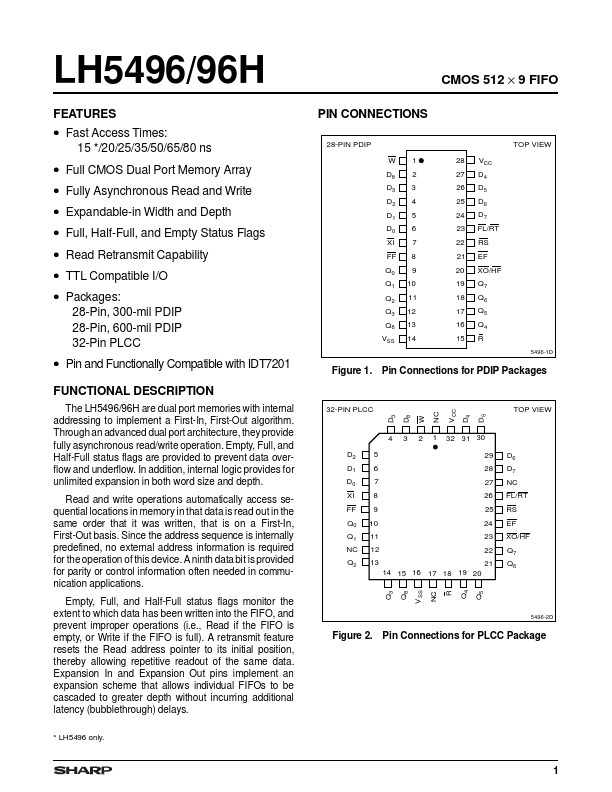

- Packages: 28-Pin, 300-mil PDIP 28-Pin, 600-mil PDIP 32-Pin PLCC

- Pin and Functionally Compatible with IDT7201 FUNCTIONAL DESCRIPTION The LH5496/96H are dual port memories with internal addressing to implement a First-In, First-Out algorithm. Through an advanced dual port architecture, they provide fully asynchronous read/write operation. Empty, Full, and Half-Full status flags are provided to prevent data overflow and underflow. In addition, internal logic provides for unlimited expansion in both word size and depth. Read and write operations automatically access sequential locations in memory in that data is read out in the same order that it was written, that is on a First-In, First-Out basis. Since the address sequence is internally predefined, no external address information is required for the operation of this device. A ninth data bit is provided for parity or control information often needed in communication applications. Empty, Full, and Half-Full status flags monitor the extent to which data has been written into the FIFO, and prevent improper operations (i.e., Read if the FIFO is empty, or Write if the FIFO is full). A retransmit feature resets the Read address pointer to its initial position, thereby allowing repetitive readout of the same data. Expansion In and Expansion Out pins implement an expansion scheme that allows individual FIFOs to be cascaded to greater depth without incurring additional latency (bubblethrough) delays.

- LH5496 only. NC CMOS 512 × 9 FIFO