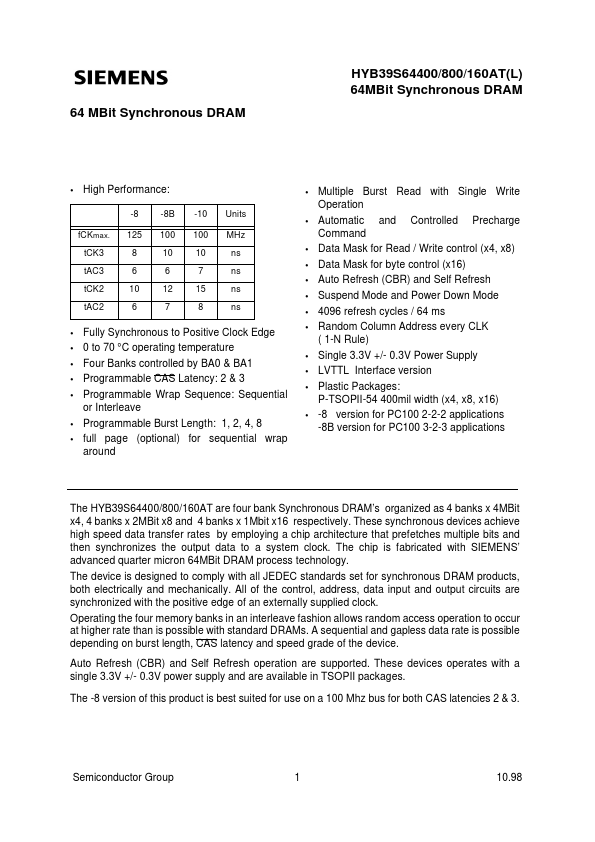

HYB39S64400 Description

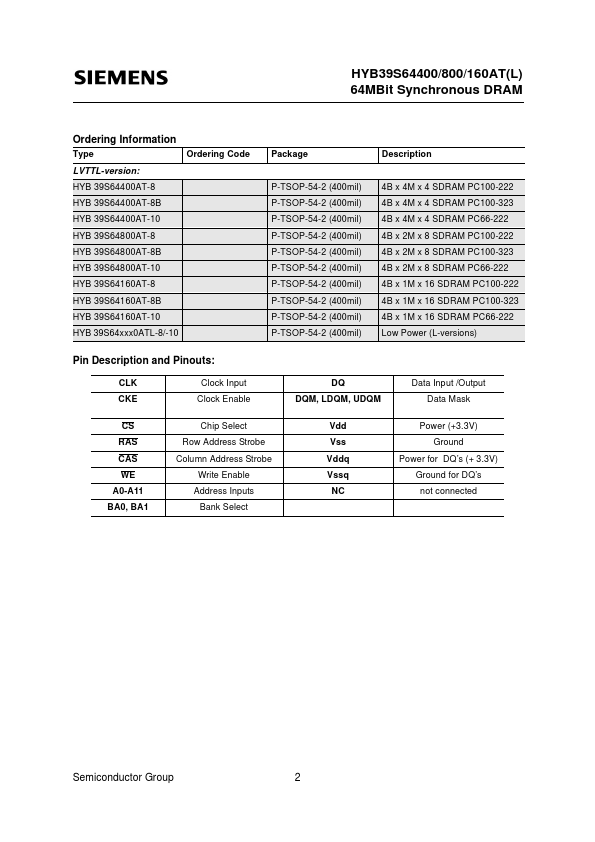

LVTTL-version: HYB 39S64400AT-8 HYB 39S64400AT-8B HYB 39S64400AT-10 HYB 39S64800AT-8 HYB 39S64800AT-8B HYB 39S64800AT-10 HYB 39S64160AT-8 HYB 39S64160AT-8B HYB 39S64160AT-10 HYB 39S64xxx0ATL-8/-10 P-TSOP-54-2 (400mil) P-TSOP-54-2 (400mil) P-TSOP-54-2 (400mil).