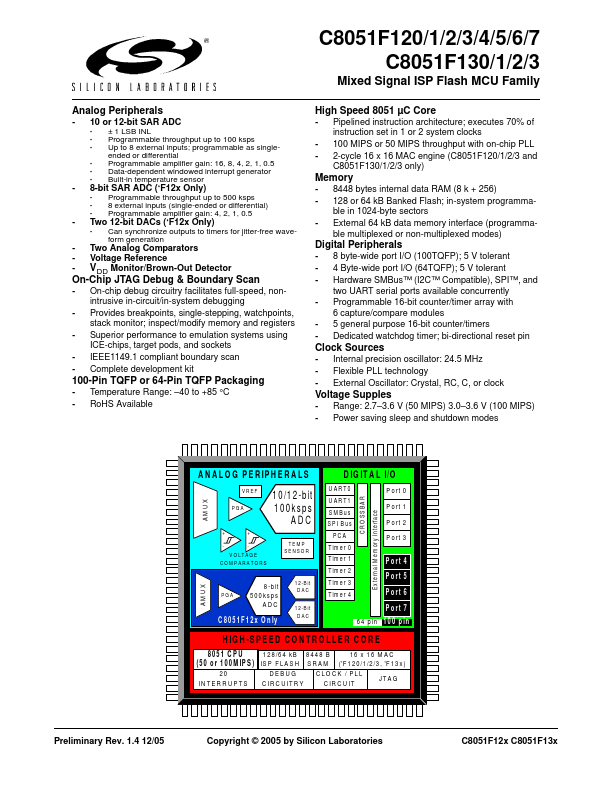

C8051F130 Description

programmable as single- ended or differential Programmable amplifier gain: 16, 8, 4, 2, 1, 0.5 Data-dependent windowed interrupt generator Built-in temperature sensor - 8-bit SAR ADC (‘F12x Only) Programmable throughput up to 500 ksps 8 external inputs (single-ended or differential) Programmable amplifier gain: 4, 2, 1, 0.5 - Two 12-bit DACs (‘F12x Only) Can synchronize outputs to timers for jitter-free waveform...