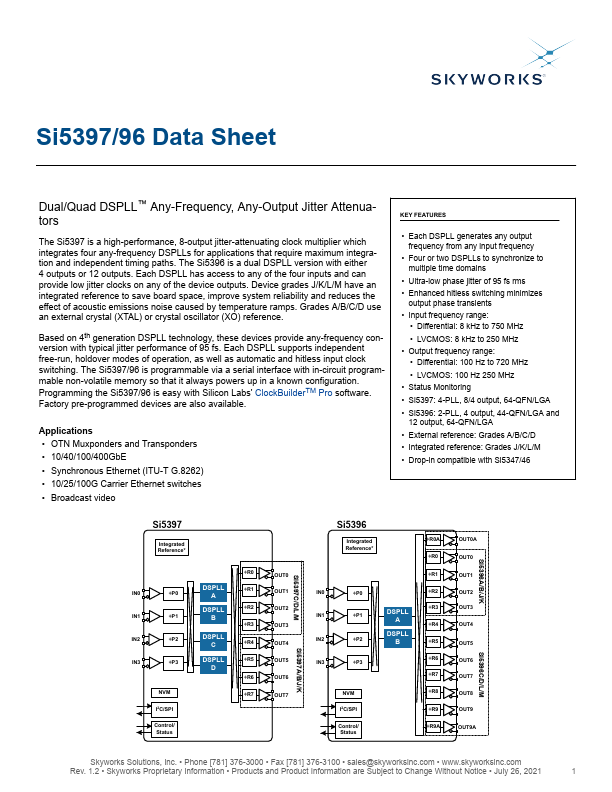

Si5397 Description

Si5397/96 Data Sheet Dual/Quad DSPLL™ Any-Frequency, Any-Output Jitter Attenuators The Si5397 is a high-performance, 8-output jitter-attenuating clock multiplier which integrates four any-frequency DSPLLs for applications that require maximum integration and independent timing paths. The Si5396 is a dual DSPLL version with either 4 outputs or 12 outputs. Each DSPLL has access to any of the four inputs and can...

Si5397 Key Features

- Each DSPLL generates any output frequency from any input frequency

- Four or two DSPLLs to synchronize to multiple time domains

- Ultra-low phase jitter of 95 fs rms

- Enhanced hitless switching minimizes

- Input frequency range

- Differential: 8 kHz to 750 MHz

- LVCMOS: 8 kHz to 250 MHz

- Output frequency range

- Differential: 100 Hz to 720 MHz

- LVCMOS: 100 Hz 250 MHz