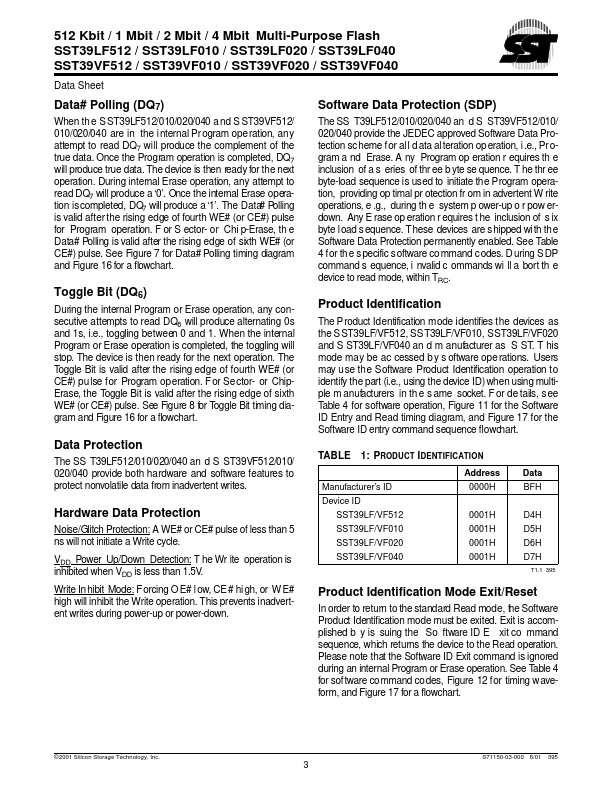

39VF010 Description

The split-gate cell design and thick oxide tunneling injector attain better reliability and manufacturability pared with alternate approaches. The SST39LF512/ 010/020/040 devices write (Program or Erase) with a 3.03.6V pow er su pply. The SS T39VF512/010/020/040 devices write with a 2.7-3.6V power supply.

39VF010 Key Features

- Single Voltage Read and Write Operations

- 3.0-3.6V for SST39LF512/010/020/040

- 2.7-3.6V for SST39VF512/010/020/040

- Superior Reliability

- Endurance: 100,000 Cycles (typical)

- Greater than 100 years Data Retention

- Low Power Consumption

- Active Current: 10 mA (typical)

- Standby Current: 1 µA (typical)

- Sector-Erase Capability