Datasheet Summary

..

THC63LVDF84B/THC63LVDF64B_Rev2.0

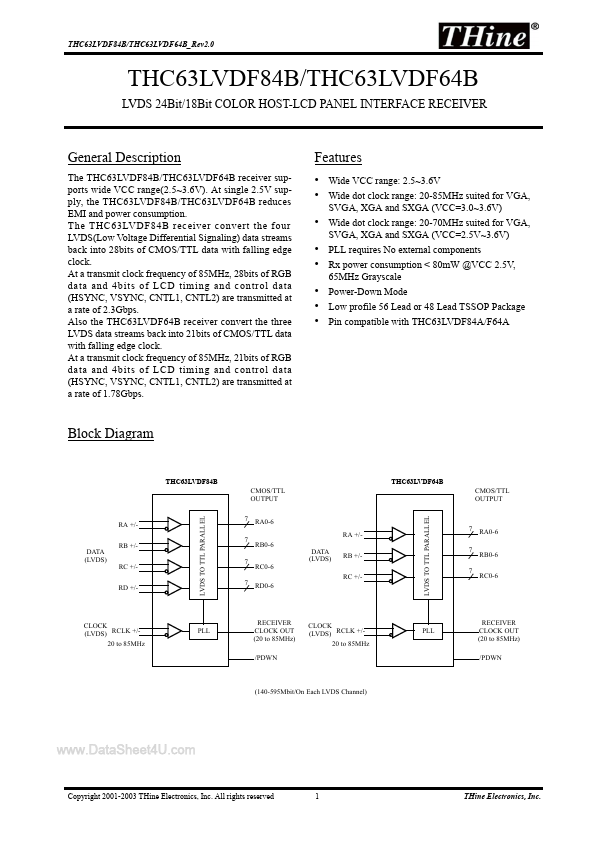

THC63LVDF84B/THC63LVDF64B

LVDS 24Bit/18Bit COLOR HOST-LCD PANEL INTERFACE RECEIVER

General Description

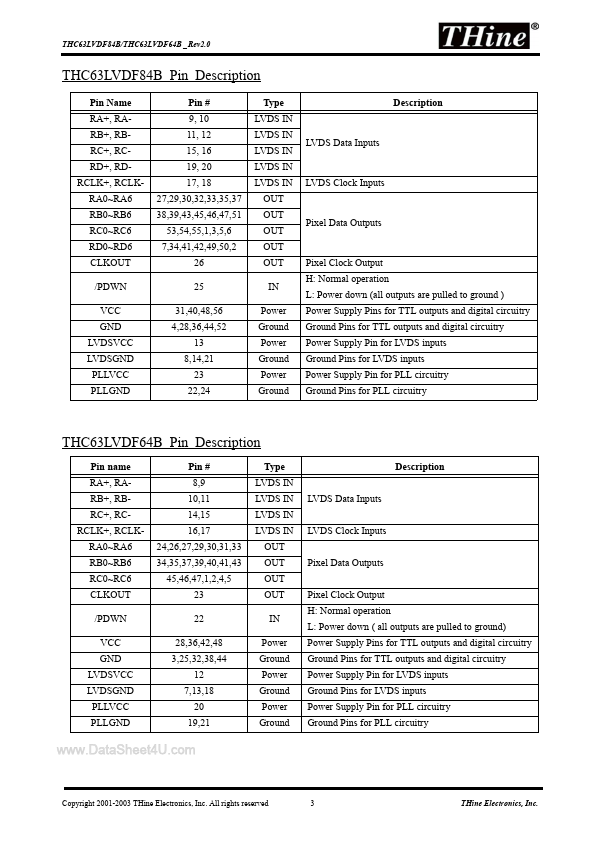

The THC63LVDF84B/THC63LVDF64B receiver supports wide VCC range(2.5~3.6V). At single 2.5V supply, the THC63LVDF84B/THC63LVDF64B reduces EMI and power consumption. The THC63LVDF84B receiver convert the four LVDS(Low Voltage Differential Signaling) data streams back into 28bits of CMOS/TTL data with falling edge clock. At a transmit clock frequency of 85MHz, 28bits of RGB data and 4bits of LCD timing and control data (HSYNC, VSYNC, CNTL1, CNTL2) are transmitted at a rate of 2.3Gbps. Also the THC63LVDF64B receiver convert the three LVDS...