74HC175D Overview

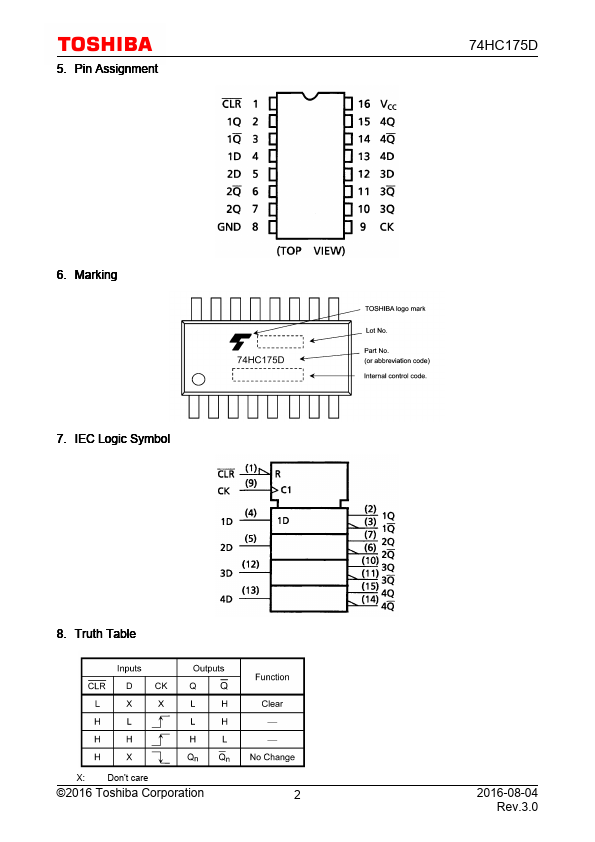

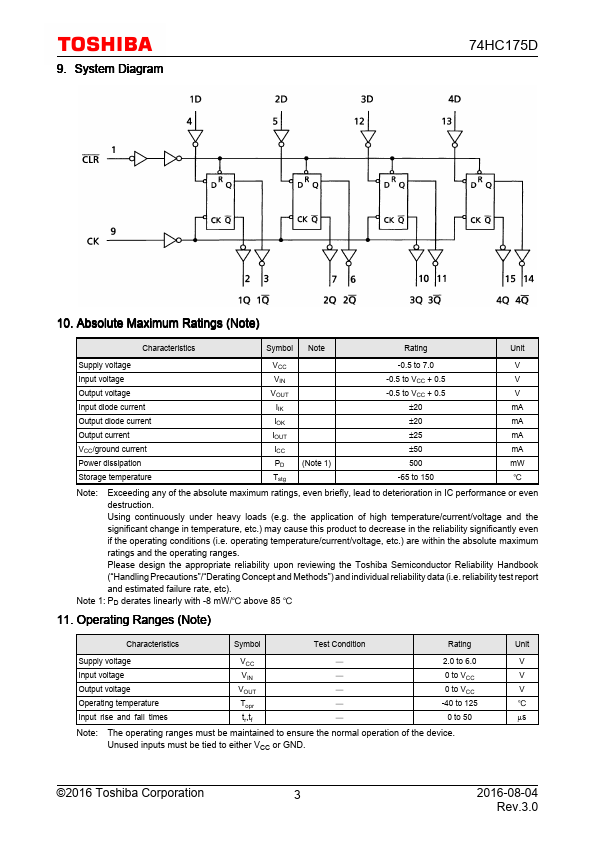

Quad D-Type Flip-Flop with Clear 2. General The 74HC175D is a high speed CMOS D-TYPE FLIP FLOP fabricated with silicon gate C2MOS technology. It achieves the high speed operation similar to equivalent LSTTL while maintaining the CMOS low power dissipation.