Datasheet Summary

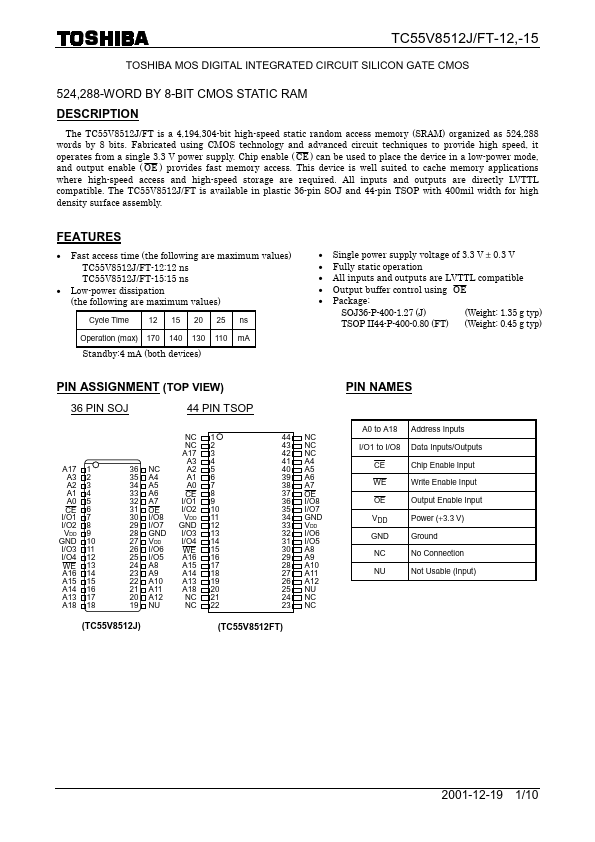

TC55V8512J/FT-12,-15

TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON GATE CMOS

524,288-WORD BY 8-BIT CMOS STATIC RAM DESCRIPTION

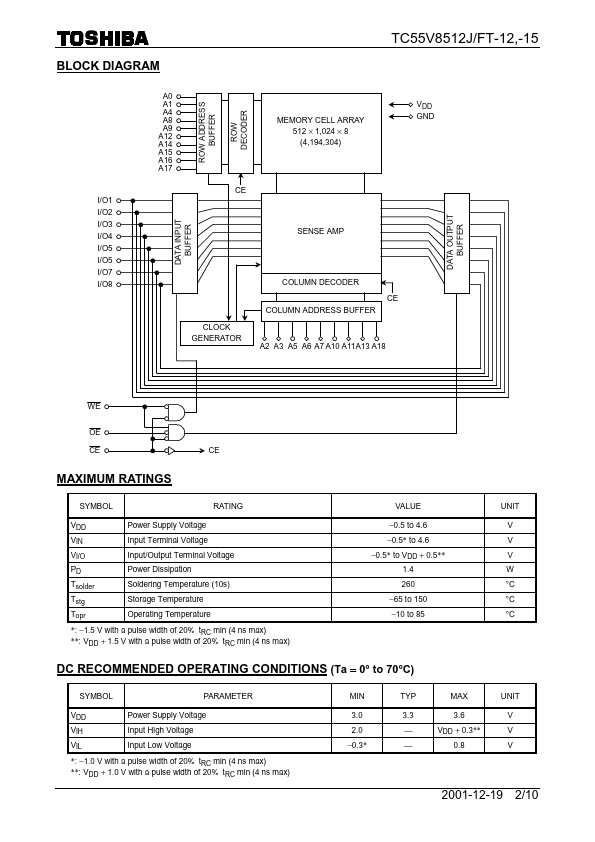

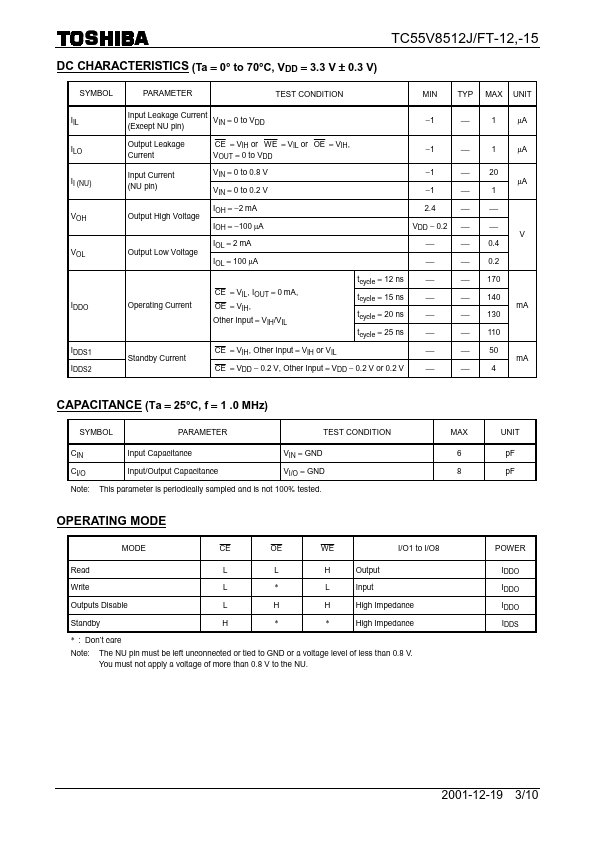

The TC55V8512J/FT is a 4,194,304-bit high-speed static random access memory (SRAM) organized as 524,288 words by 8 bits. Fabricated using CMOS technology and advanced circuit techniques to provide high speed, it operates from a single 3.3 V power supply. Chip enable ( CE ) can be used to place the device in a low-power mode, and output enable ( OE ) provides fast memory access. This device is well suited to cache memory applications where high-speed access and high-speed storage are required. All inputs and outputs are directly LVTTL patible. The TC55V8512J/FT...