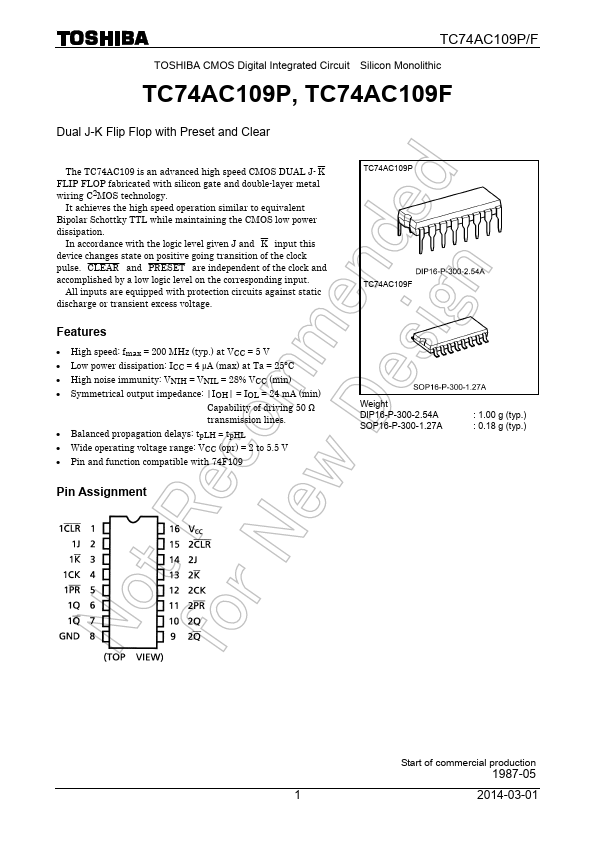

TC74AC109F

Key Features

- High speed: fmax = 200 MHz (typ.) at VCC = 5 V

- Low power dissipation: ICC = 4 μA (max) at Ta = 25°C

- High noise immunity: VNIH = VNIL = 28% VCC (min)

- Symmetrical output impedance: |IOH| = IOL = 24 mA (min) Capability of driving 50 Ω transmission lines

- Balanced propagation delays: tpLH ∼- tpHL

- Wide operating voltage range: VCC (opr) = 2 to 5.5 V