Datasheet Summary

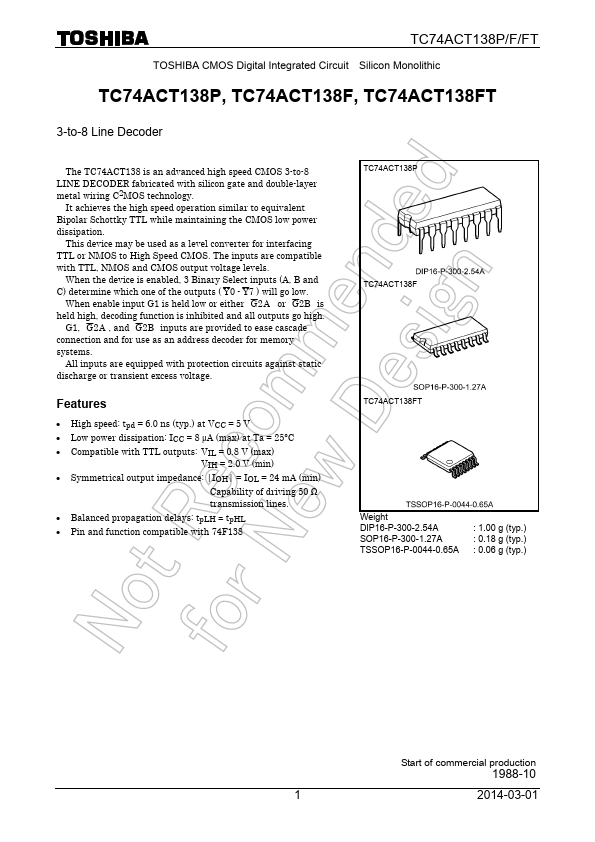

TC74ACT138P/F/FT

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

TC74ACT138P, TC74ACT138F, TC74ACT138FT

3-to-8 Line Decoder

The TC74ACT138 is an advanced high speed CMOS 3-to-8 LINE DECODER fabricated with silicon gate and double-layer metal wiring C2MOS technology.

It achieves the high speed operation similar to equivalent Bipolar Schottky TTL while maintaining the CMOS low power dissipation.

This device may be used as a level converter for interfacing TTL or NMOS to High Speed CMOS. The inputs are patible with TTL, NMOS and CMOS output voltage levels.

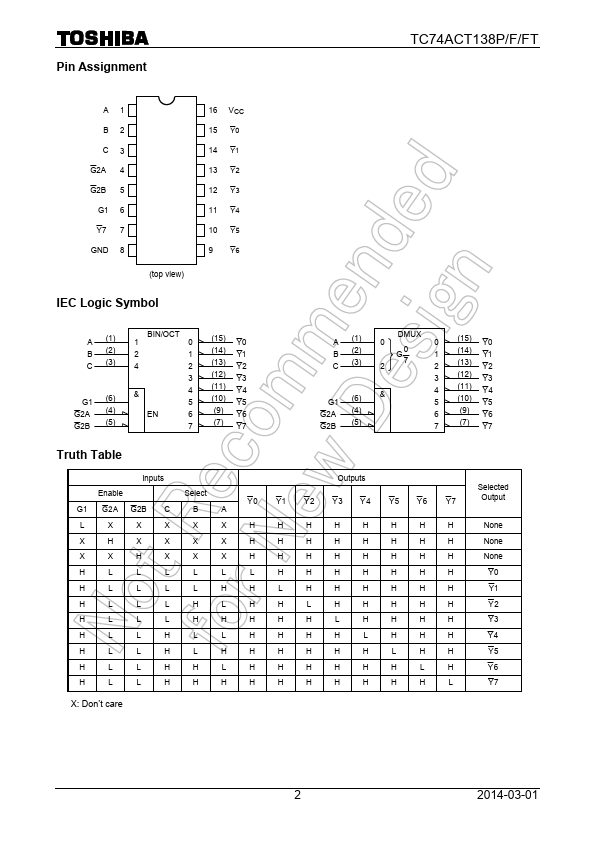

When the device is enabled, 3 Binary Select inputs (A, B and C) determine which one of the outputs ( Y0

- Y7 ) will go...