Datasheet Summary

TC74LVX138F/FT

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

TC74LVX138F, TC74LVX138FT

3-to-8 Line Decoder

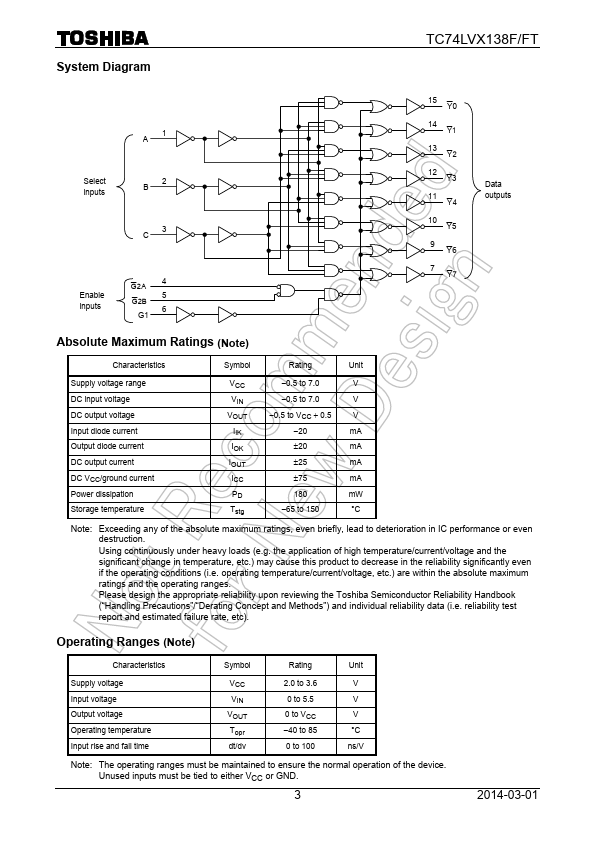

The TC74LVX138F/ FT is a high-speed CMOS 3-to-8 line decoder fabricated with silicon gate CMOS technology. Designed for use in 3-V systems, it achieves high-speed operation while maintaining the CMOS low power dissipation.

This device is suitable for low-voltage and battery operated systems.

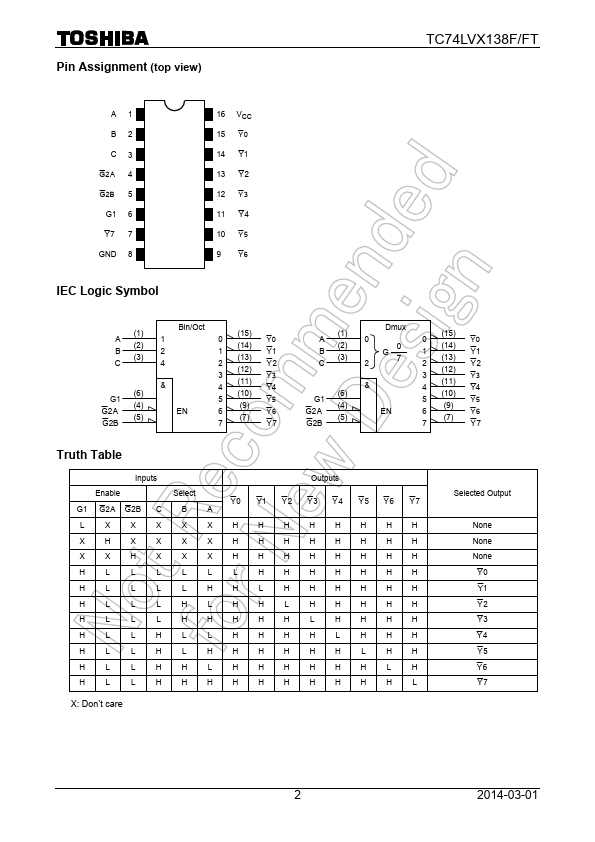

When the device is enabled, 3 Binary Select inputs (A, B and C) determine which one of the outputs ( Y0

- Y7 ) will go low. When enable input G1 is held low or either G2A or G2B is held high, decoding function is inhibited and all outputs go high.

G1, G2A , and G2B inputs are...