TQ8101C Description

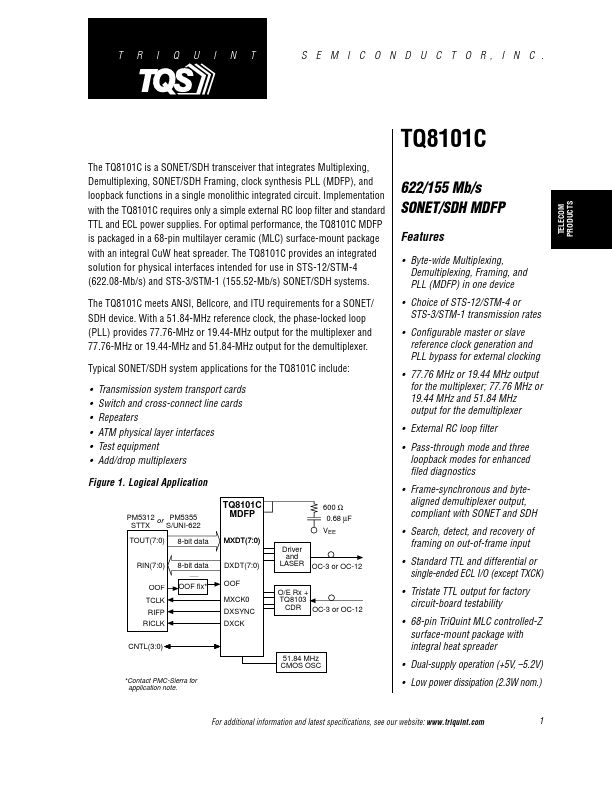

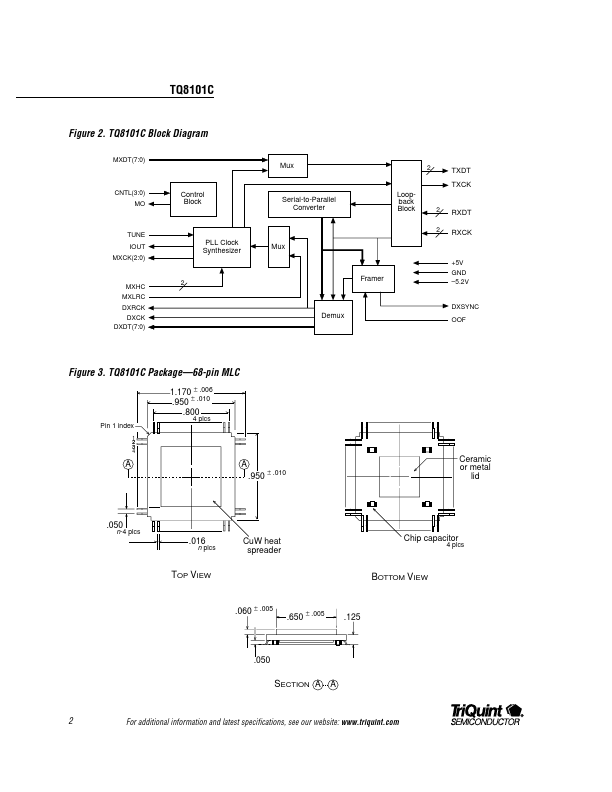

T R I Q U I N T S E M I C O N D U C T O R, I N C . TQ8101C The TQ8101C is a SONET/SDH transceiver that integrates Multiplexing, Demultiplexing, SONET/SDH Framing, clock synthesis PLL (MDFP), and loopback functions in a single monolithic integrated circuit. Implementation with the TQ8101C requires only a simple external RC loop filter and standard TTL and ECL power supplies.

TQ8101C Key Features

- Byte-wide Multiplexing, Demultiplexing, Framing, and PLL (MDFP) in one device

- Choice of STS-12/STM-4 or STS-3/STM-1 transmission rates

- Configurable master or slave reference clock generation and PLL bypass for external clocking

- 77.76 MHz or 19.44 MHz output for the multiplexer; 77.76 MHz or 19.44 MHz and 51.84 MHz output for the demultiplexer

- External RC loop filter

- Pass-through mode and three loopback modes for enhanced filed diagnostics

- Frame-synchronous and bytealigned demultiplexer output, pliant with SONET and SDH

- Search, detect, and recovery of framing on out-of-frame input

- Standard TTL and differential or single-ended ECL I/O (except TXCK)

- Tristate TTL output for factory circuit-board testability

TQ8101C Applications

- Byte-wide Multiplexing, Demultiplexing, Framing, and PLL (MDFP) in one device