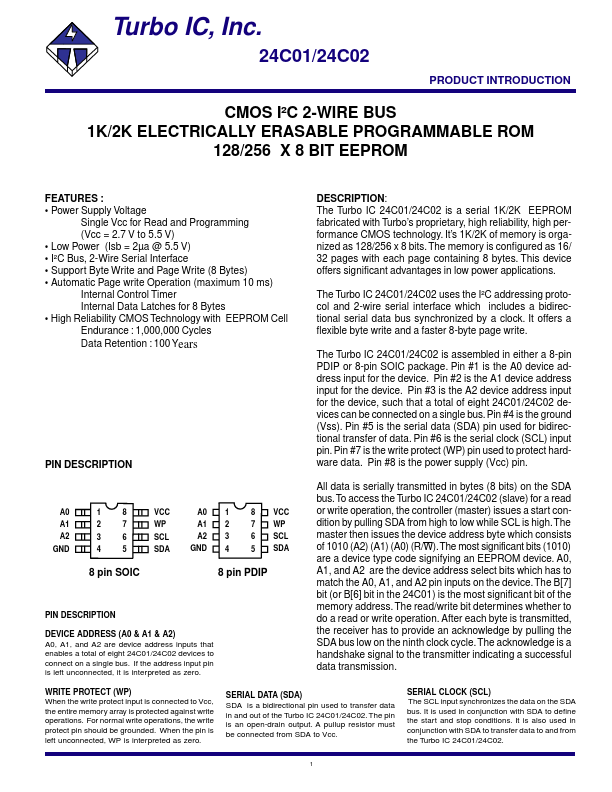

24C02 Overview

The Turbo IC 24C01/24C02 is a serial 1K/2K EEPROM fabricated with Turbo’s proprietary, high reliability, high performance CMOS technology. It’s 1K/2K of memory is organized as 128/256 x 8 bits. The memory is configured as 16/ 32 pages with each page containing 8 bytes.

24C02 Key Features

- Power Supply Voltage Single Vcc for Read and Programming (Vcc = 2.7 V to 5.5 V)

- Low Power (Isb = 2µa @ 5.5 V)

- I²C Bus, 2-Wire Serial Interface

- Support Byte Write and Page Write (8 Bytes)

- Automatic Page write Operation (maximum 10 ms) Internal Control Timer Internal Data Latches for 8 Bytes