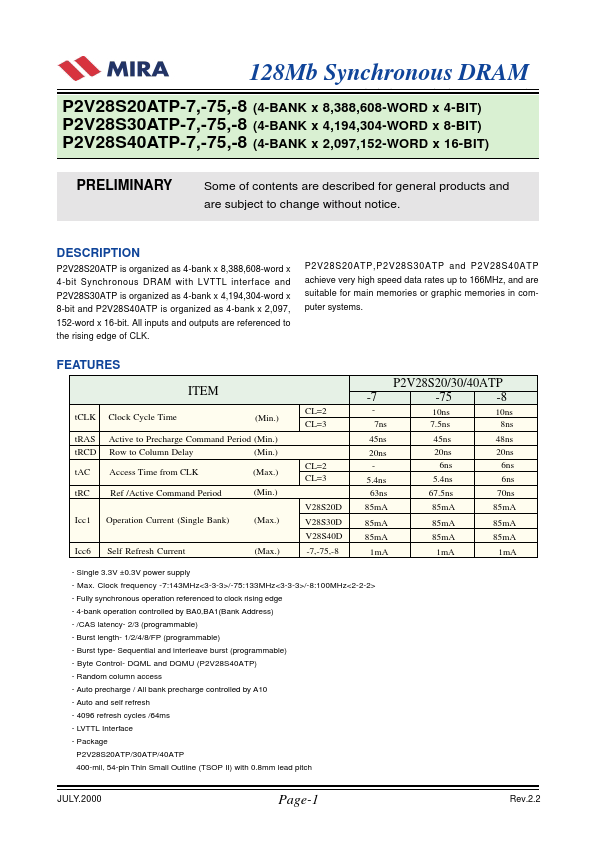

P2V28S20DTP-7 Overview

All inputs and outputs are referenced to the rising edge of CLK. P2V28S20ATP,P2V28S30ATP and P2V28S40ATP achieve very high speed data rates up to 166MHz, and are suitable for main memories or graphic memories in puter systems.

P2V28S20DTP-7 Key Features

- Single 3.3V ±0.3V power supply

- Max. Clock frequency -7:143MHz<3-3-3>/-75:133MHz<3-3-3>/-8:100MHz<2-2-2>

- Fully synchronous operation referenced to clock rising edge

- 4-bank operation controlled by BA0,BA1(Bank Address)

- /CAS latency- 2/3 (programmable)

- Burst length- 1/2/4/8/FP (programmable)

- Burst type- Sequential and interleave burst (programmable)

- Byte Control- DQML and DQMU (P2V28S40ATP)

- Random column access

- Auto precharge / All bank precharge controlled by A10