Datasheet Summary

..

White Electronic Designs

ADVANCED-

2x128Kx72, 3.3V Sync/Sync Burst SRAM SO-DIMM

Features

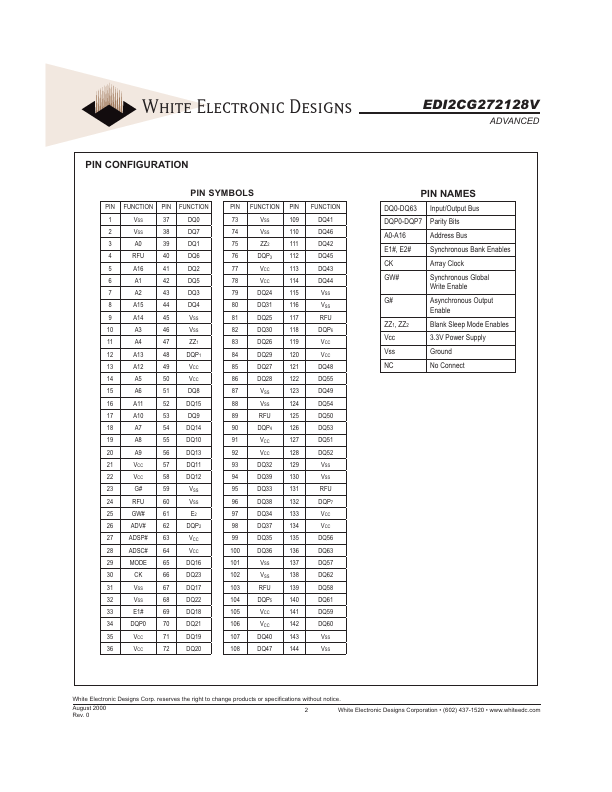

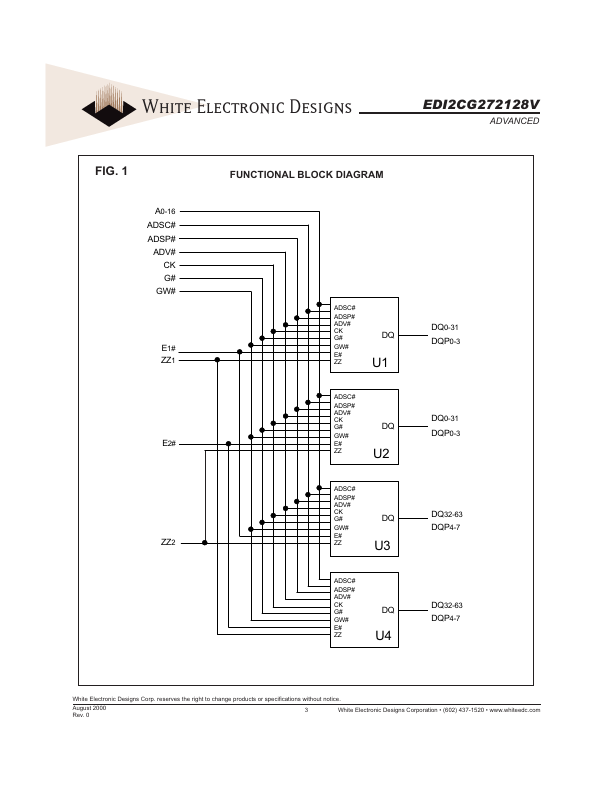

2x128Kx72 Synchronous, Synchronous Burst Flow-Through Architecture Linear and Sequential Burst Support via MODE pin Access Speed(s): TKHQV = 8.5, 9, 12, 15ns Clock Controlled Registered Bank Enables (E1#, E2#) Clock Controlled Registered Address Clock Controlled Registered Global Write (GW#) Aysnchronous Output Enable (G#) Internally Self-timed Write Individual Bank Sleep Mode enables (ZZ1, ZZ2) Gold Lead Finish 3.3V ± 10% Operation mon Data I/O High Capacitance (30pf) drive, at rated Access Speed Single Total Array Clock Multiple Vcc and Gnd

DESCRIPTION

The...