WED3EG7233S-D3

Overview

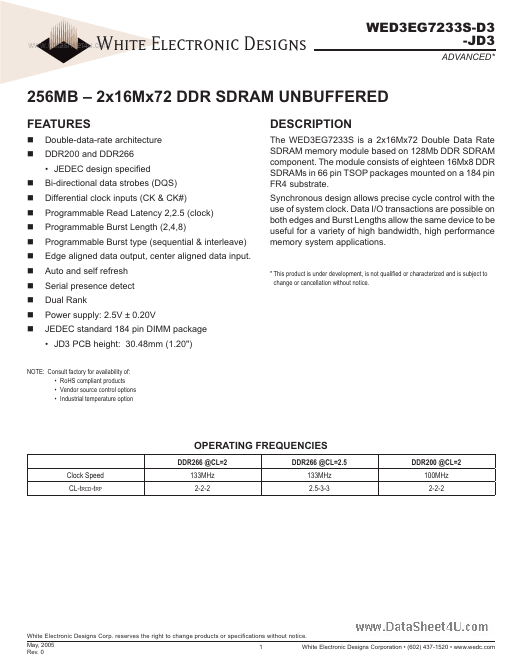

The WED3EG7233S is a 2x16Mx72 Double Data Rate SDRAM memory module based on 128Mb DDR SDRAM component. The module consists of eighteen 16Mx8 DDR SDRAMs in 66 pin TSOP packages mounted on a 184 pin FR4 substrate.

- JEDEC design specified Bi-directional data strobes (DQS) Differential clock inputs (CK & CK#) Programmable Read Latency 2,2.5 (clock) Programmable Burst Length (2,4,8) Programmable Burst type (sequential & interleave) Edge aligned data output, center aligned data input. Auto and self refresh Serial presence detect Dual Rank Power supply: 2.5V ± 0.20V JEDEC standard 184 pin DIMM package

- JD3 PCB height: 30.48mm (1.20") NOTE: Consult factory for availability of:

- RoHS compliant products

- Vendor source control options

- Industrial temperature option * This product is under development, is not qualified or characterized and is subject to change or cancellation without notice.