| Part | WSE128K16-xxx |

|---|---|

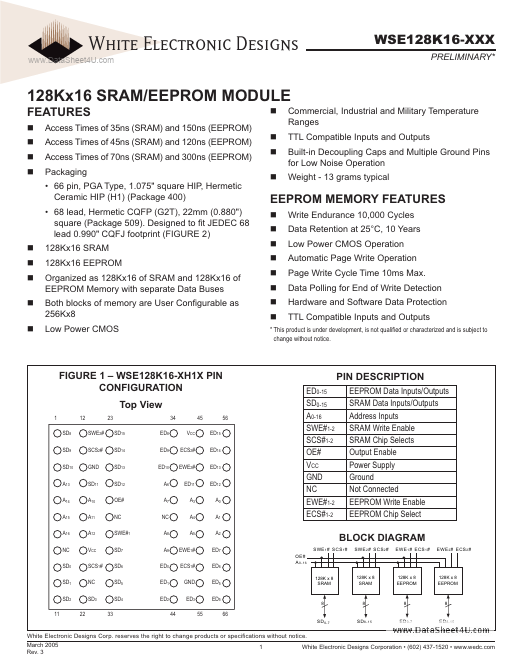

| Description | 128Kx16 SRAM/EEPROM MODULE |

| Category | EEPROM |

| Manufacturer | White Electronic Designs Corporation |

| Size | 611.35 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| HFDOM40B-xxxSx | Hanbit Electronics | 40Pin Flash Disk Module |

| HFDOM44P-xxxSx | Hanbit Electronics | 44Pin Flash Disk Module |

| HFDOM40P-xxxSx | Hanbit Electronics | 40Pin Flash Disk Module |