Datasheet Summary

W5100 Datasheet

Version 1.2.8

© 2011 WIZnet Co., Inc. All Rights Reserved. For more information, visit our website at http://.wiznet.co.kr

© Copyright 2009-2011 WIZnet Co., Inc. All rights reserved.

W5100 Datasheet

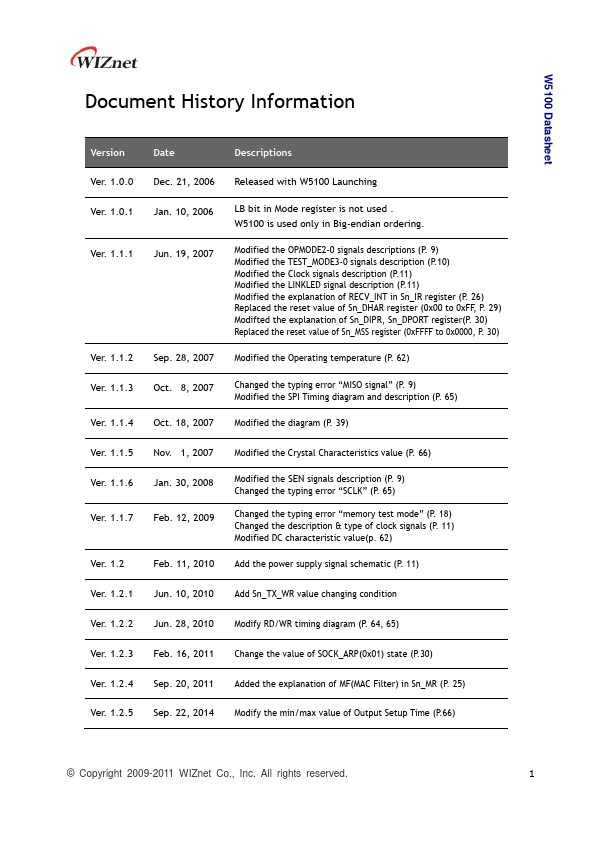

Document History Information

Version

Date

Descriptions

Ver. 1.0.0 Dec. 21, 2006 Released with W5100 Launching

Ver. 1.0.1

Jan. 10, 2006

LB bit in Mode register is not used . W5100 is used only in Big-endian ordering.

Ver. 1.1.1

Jun. 19, 2007

Modified the OPMODE2-0 signals descriptions (P. 9) Modified the TEST_MODE3-0 signals description (P.10) Modified the Clock signals description (P.11) Modified the LINKLED signal description (P.11) Modified the explanation of...