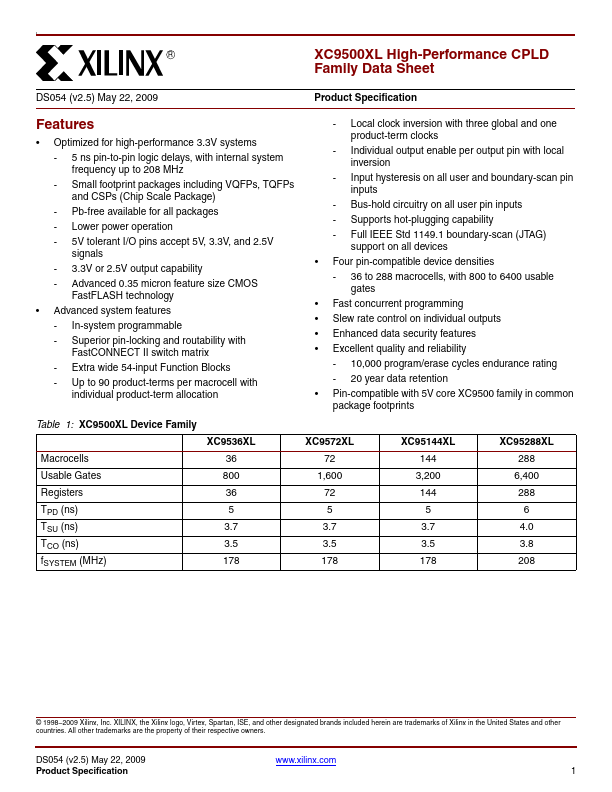

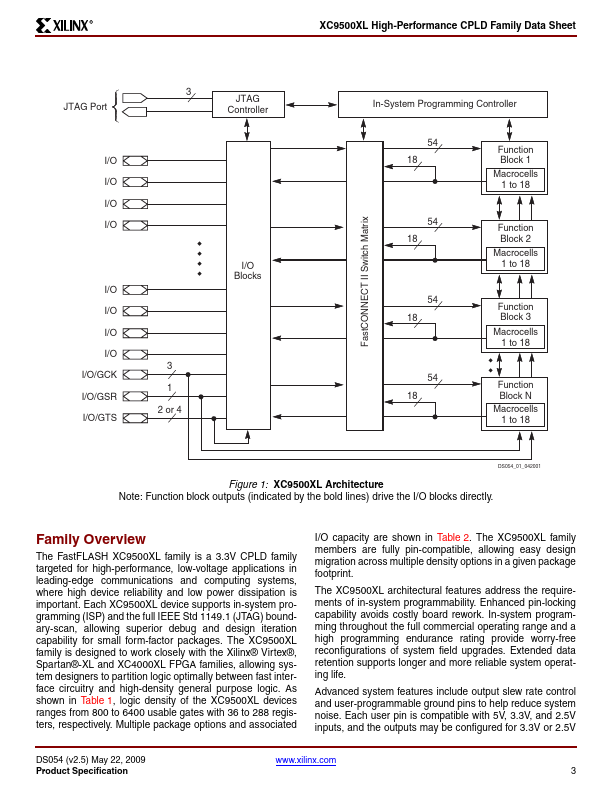

XC9500XL Description

k 0 R XC9500XL High-Performance CPLD Family Data Sheet DS054 (v2.5) May 22, 2009 0 0 Product Specification.

XC9500XL Key Features

- Optimized for high-performance 3.3V systems

- 5 ns pin-to-pin logic delays, with internal system frequency up to 208 MHz

- Small footprint packages including VQFPs, TQFPs and CSPs (Chip Scale Package)

- Pb-free available for all packages

- Lower power operation

- 5V tolerant I/O pins accept 5V, 3.3V, and 2.5V signals

- 3.3V or 2.5V output capability

- Advanced 0.35 micron feature size CMOS FastFLASH technology

- Advanced system features

- In-system programmable