YSS922 Description

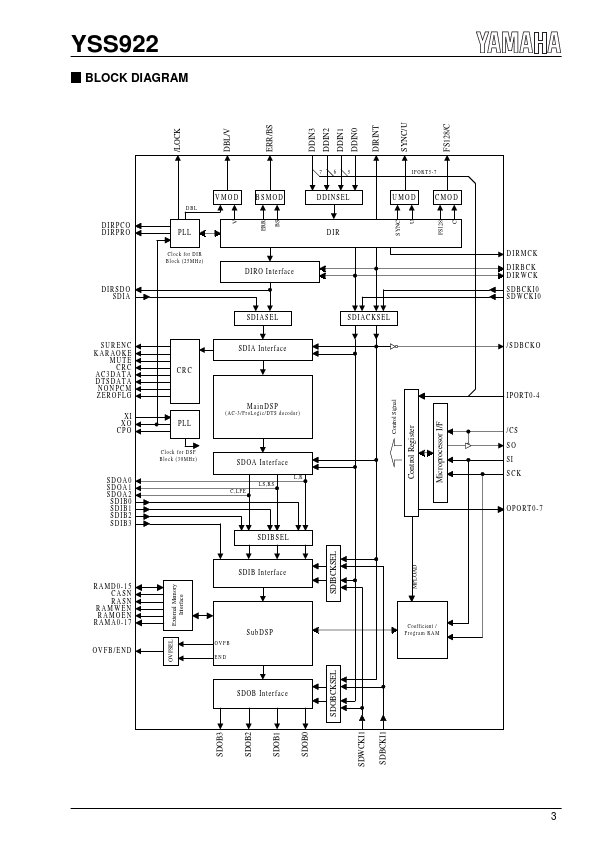

YSS922 AC3D3 OUTLINE 96kHz sampling frequency. Preliminary 96kHz DIR + Dolby Digital / Pro Logic / DTS decoder + Sub DSP YSS922 is one chip LSI consisting of three built-in blocks : Dolby Digital (AC-3) / Pro Logic & DTS decoder (Main DSP), a programmable sound processing DSP (Sub DSP) and SPDIF receiver (DIR) which can handle up to The Sub DSP is capable of realizing various sound fields, such as virtual surround...

YSS922 Key Features

- Sampling frequency: two ranges are available including; 32k to 48kHz (normal rate) and 64k to 96kHz (double rate)

- Provides master clock, 256fs, to DAC, ADC and other peripheral devices. The clock output can be controlled with various

- Has a pin that indicates the double rate operation

- Every channel status and user data can be read through the microprocessor interface

- Has an output pin for interrupt that is activated by changing of the status information

- Internal operation frequency: 25MHz

- Dolby Digital (AC-3) / Pro Logic and DTS decode

- High quality internal 24 bit DSP

- No external memory is required. (Memory for center and surround channel delay is included.)

- AC-3 Karaoke mode