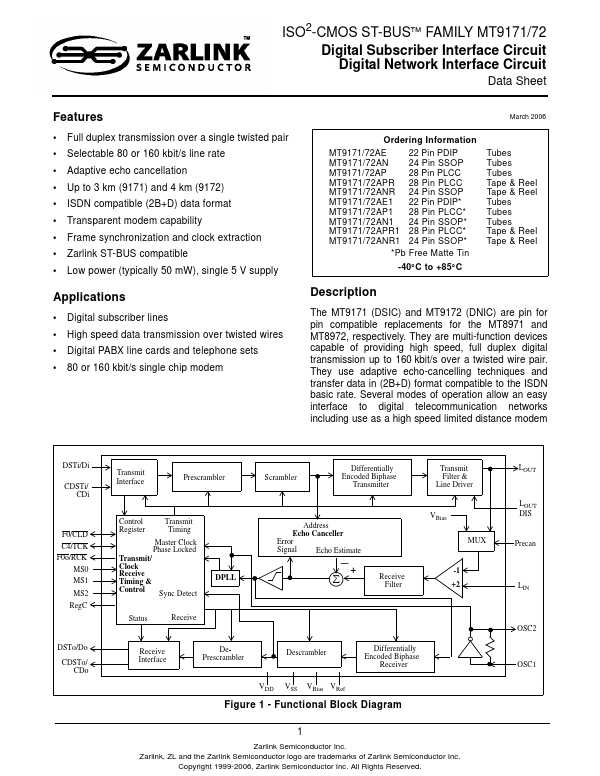

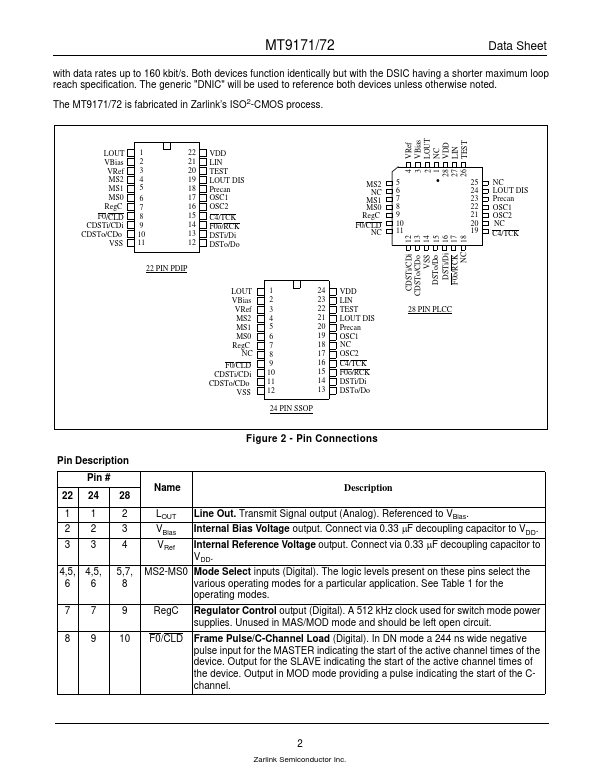

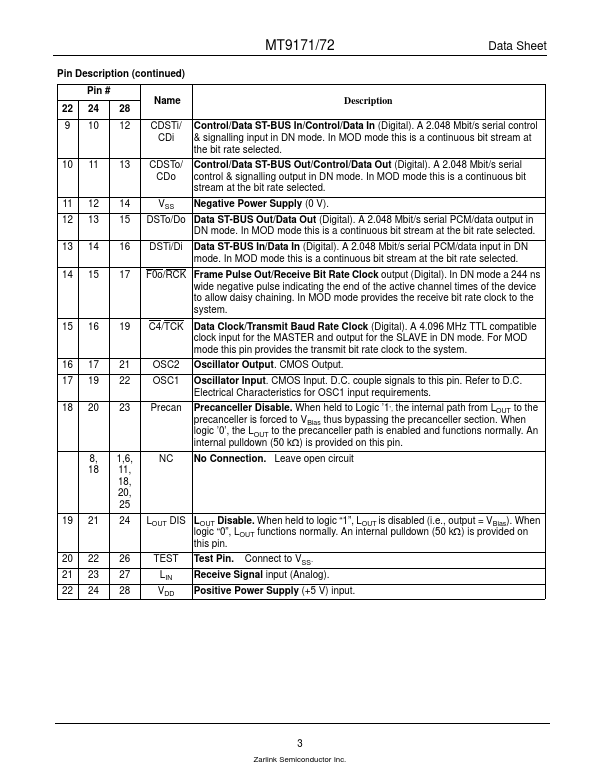

Datasheet Summary

ISO2-CMOS ST-BUS FAMILY MT9171/72 Digital Subscriber Interface Circuit Digital Network Interface Circuit

Features

- -

- -

- -

- -

- Full duplex transmission over a single twisted pair Selectable 80 or 160 kbit/s line rate Adaptive echo cancellation Up to 3km (9171) and 4 km (9172) ISDN patible (2B+D) data format Transparent modem capability Frame synchronization and clock extraction Zarlink ST-BUS patible Low power (typically 50 mW), single 5V supply

DS5130 ISSUE 3 February 1999

Ordering Information MT9171AE 22 Pin Plastic DIP (400 mil) MT9171AN 24 Pin SSOP MT9171AP 28 Pin PLCC MT9172AE 22 Pin Plastic DIP (400 mil) MT9172AN 24 Pin SSOP MT9172AP 28 Pin PLCC -40°C to + 85°C

Descriptio...