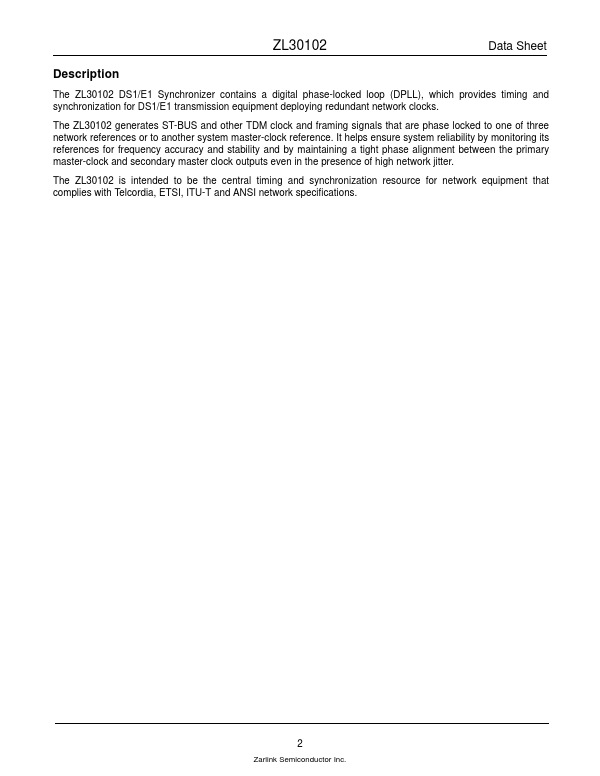

ZL30102 Description

The ZL30102 DS1/E1 Synchronizer contains a digital phase-locked loop (DPLL), which provides timing and synchronization for DS1/E1 transmission equipment deploying redundant network clocks. The ZL30102 generates ST-BUS and other TDM clock and framing signals that are phase locked to one of three network references or to another system master-clock reference. It helps ensure system reliability by monitoring its...

ZL30102 Key Features

- Synchronizes to clock-and-sync-pair to maintain minimal phase skew between an H.110 primary master clock and a secondary

- Supports Telcordia GR-1244-CORE Stratum 4 and 4E

- Supports ITU-T G.823 and G.824 for 2048 kbit/s and 1544 kbit/s interfaces

- Supports ANSI T1.403 and ETSI ETS 300 011 for ISDN primary rate interfaces

- Simple hardware control interface

- Manual and Automatic hitless reference switching between any bination of valid input reference frequencies

- Accepts three input references and synchronizes to any bination of 8 kHz, 1.544 MHz, 2.048 MHz, 8.192 MHz or 16.384 MHz

- Provides 5 styles of 8 kHz framing pulses

- Holdover frequency accuracy of 1x10-7

- Provides Lock, Holdover and selectable Out of Range indication

ZL30102 Applications

- Synchronization and timing control for multi-trunk DS1/ E1 terminal systems such as DSLAMs, Gateways and PBXs

- Clock and frame pulse source for H.110 CT Bus, ST-BUS, GCI and other time division multiplex (TDM) buses