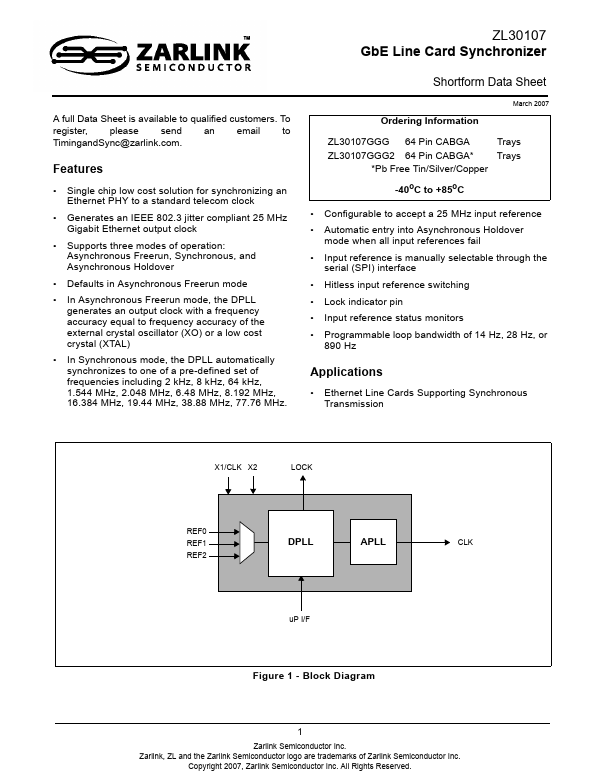

ZL30107 Overview

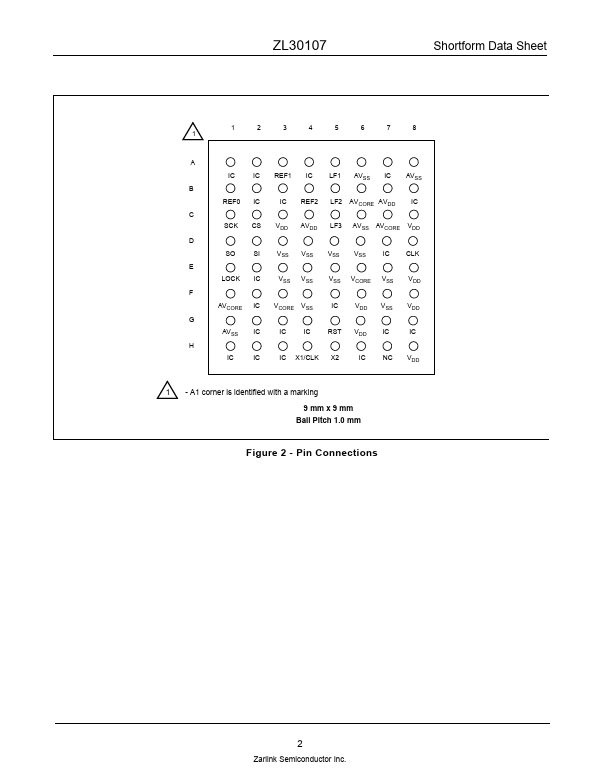

Pin # B1 A3 B4 D8 G5 Name REF0 REF1 REF2 CLK RST I/O Type Id Description Shortform Data Sheet Reference Inputs (LVCMOS, Schmitt Trigger). These reference inputs are used for synchronizing the PLL. These pins are internally pulled down to Vss.