74HCT237

74HCT237 is High-Speed CMOS Logic 3 to 8-Line Decoder/Demultiplexer manufactured by Texas Instruments.

- Part of the 74HC237 comparator family.

- Part of the 74HC237 comparator family.

Data sheet acquired from Harris Semiconductor SCHS146F

March 1998

- Revised October 2003

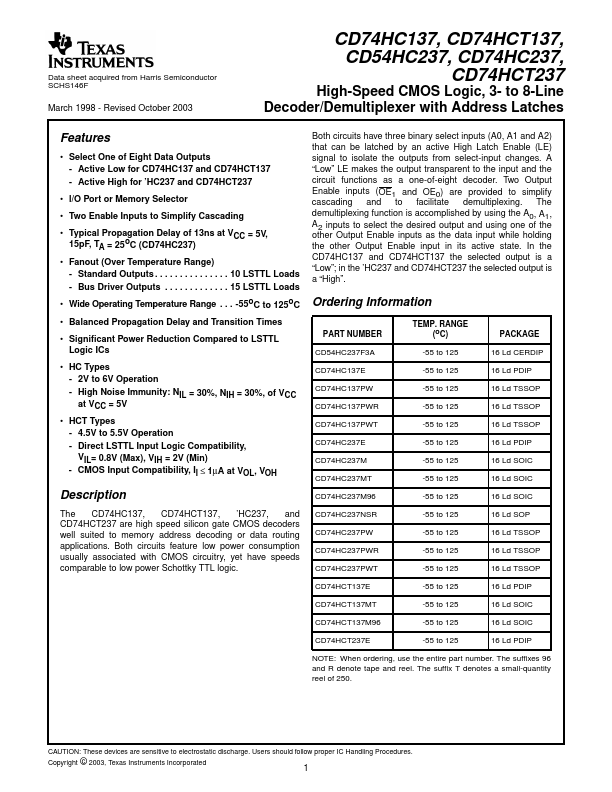

CD74HC137, CD74HCT137, CD54HC237, CD74HC237, CD74HCT237

High-Speed CMOS Logic, 3- to 8-Line

Decoder/Demultiplexer with Address Latches

[ /Title (CD74 HC137 , CD74 HCT13 7, CD74 HC237 , CD74 HCT23 7) /Subject (High Speed

Features

- Select One of Eight Data Outputs

- Active Low for CD74HC137 and CD74HCT137

- Active High for ’HC237 and CD74HCT237

- l/O Port or Memory Selector

- Two Enable Inputs to Simplify Cascading

- Typical Propagation Delay of 13ns 15pF, TA = 25oC (CD74HC237) at

=

5V,

- Fanout (Over Temperature Range)

- Standard Outputs

- -

- 10 LSTTL Loads

-...