ADS4229

Overview

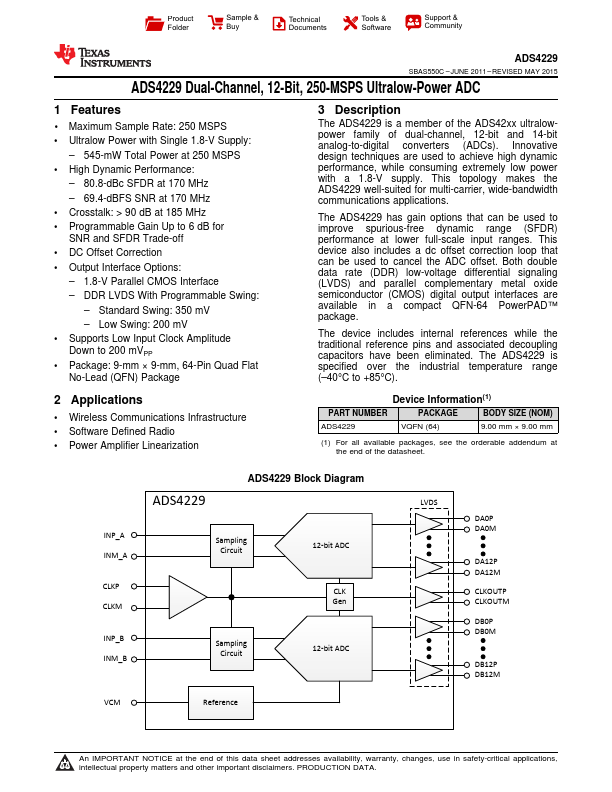

The ADS4229 is a member of the ADS42xx ultralowpower family of dual-channel, 12-bit and 14-bit analog-to-digital converters (ADCs). Innovative design techniques are used to achieve high dynamic performance, while consuming extremely low power with a 1.8-V supply.

- 1 Maximum Sample Rate: 250 MSPS

- Ultralow Power with Single 1.8-V Supply: - 545-mW Total Power at 250 MSPS

- High Dynamic Performance: - 80.8-dBc SFDR at 170 MHz - 69.4-dBFS SNR at 170 MHz

- Crosstalk: > 90 dB at 185 MHz

- Programmable Gain Up to 6 dB for SNR and SFDR Trade-off

- DC Offset Correction

- Output Interface Options: - 1.8-V Parallel CMOS Interface - DDR LVDS With Programmable Swing: - Standard Swing: 350 mV - Low Swing: 200 mV

- Supports Low Input Clock Amplitude Down to 200 mVPP

- Package: 9-mm × 9-mm, 64-Pin Quad Flat No-Lead (QFN) Package