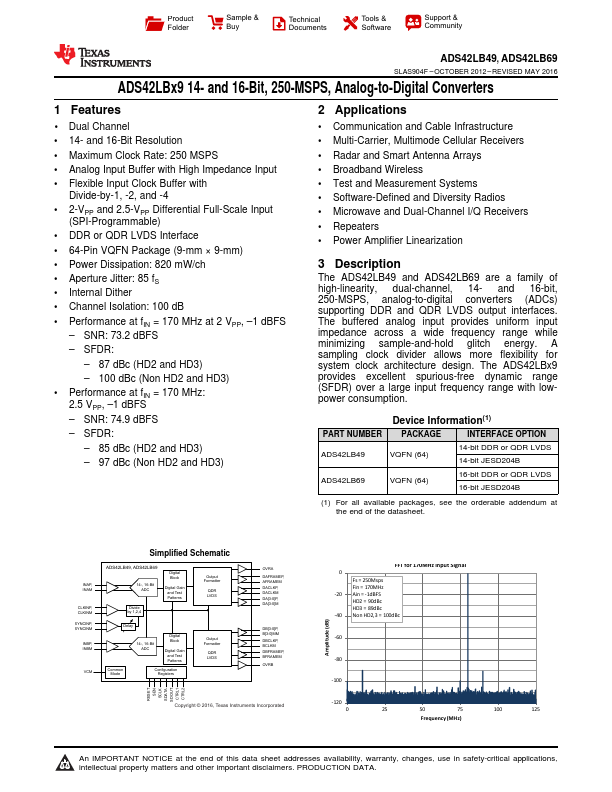

ADS42LB69 Description

The ADS42LB49 and ADS42LB69 are a family of high-linearity, dual-channel, 14- and 16-bit, 250-MSPS, analog-to-digital converters (ADCs) supporting DDR and QDR LVDS output interfaces. The buffered analog input provides uniform input impedance across a wide frequency range while minimizing sample-and-hold glitch energy. A sampling clock divider allows more flexibility for system clock architecture design.

ADS42LB69 Key Features

- 1 Dual Channel

- 14- and 16-Bit Resolution

- Maximum Clock Rate: 250 MSPS

- Analog Input Buffer with High Impedance Input

- 2-VPP and 2.5-VPP Differential Full-Scale Input

- DDR or QDR LVDS Interface

- 64-Pin VQFN Package (9-mm × 9-mm)

- Power Dissipation: 820 mW/ch

- Aperture Jitter: 85 fS

- Internal Dither