ADS54J54

ADS54J54 is Quad Channel 14-Bit 500 MSPS ADC manufactured by Texas Instruments.

Features

- 1 4 Channel, 14-Bit 500 MSPS ADC

- Analog input buffer with high impedance input

- Flexible input clock buffer with divide by 1/2/4

- 1.25 VPP Differential full-scale input

- JESD204B Serial interface

- Subclass 1 pliant up to 5 Gbps

- 1 Lane Per ADC up to 250 Msps

- 2 Lanes Per ADC up to 500 Msps

- 64-Pin QFN Package (9 mm x 9 mm)

- Key specifications:

- Power dissipation: 875 m W/ch

- Input bandwidth (3 d B): 900 MHz

- Aperture jitter: 98 fs rms

- Channel isolation: 85 d B

- Performance at ƒin = 170 MHz at 1.25 VPP,

1lane 2x Decimation

- 1 d BFS

- SNR: 67.2 d BFS

- SFDR: 85 d Bc HD2,3; 95 d BFS non-HD2,3

- Performance at ƒin = 370 MHz at 1.25 VPP, 2lane no Decimation

- 1 d BFS

- SNR: 64.7 d BFS

- SFDR: 75 d Bc HD2,3; 83 d BFS non-HD2,3

2 Applications

- Multi-Carrier, Multi-Mode, Multi-Band Cellular Receivers

- TDD-LTE, FDD-LTE, CDMA, WCMDA, CMDA2k, GSM

- Microwave backhaul

- Wireless repeaters

- Distributed antenna systems (DAS)

- Broadband wireless

- Ultra-wide band software defined radio

- Data acquisition

- Test and measurement instrumentation

- Signal intelligence and jamming

- Radar and satellite systems

- Cable infrastructure

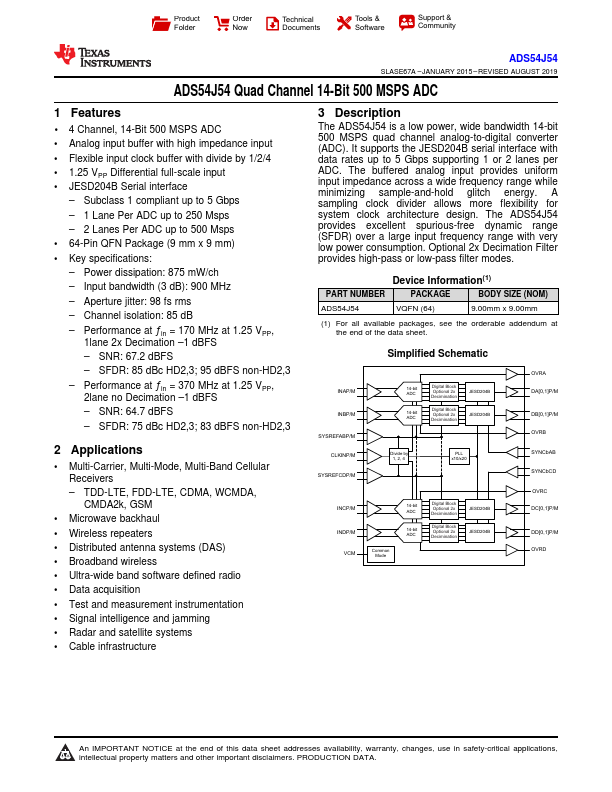

3 Description

The ADS54J54 is a low power, wide bandwidth 14-bit 500 MSPS quad channel analog-to-digital converter (ADC). It supports the JESD204B serial interface with data rates up to 5 Gbps supporting 1 or 2 lanes per ADC. The buffered analog input provides uniform input impedance across a wide frequency range while minimizing sample-and-hold glitch energy. A sampling clock divider allows more flexibility for system clock architecture design. The ADS54J54 provides excellent spurious-free dynamic range (SFDR) over a large input frequency range with very low power consumption. Optional 2x Decimation Filter provides high-pass or low-pass filter modes.

Device...