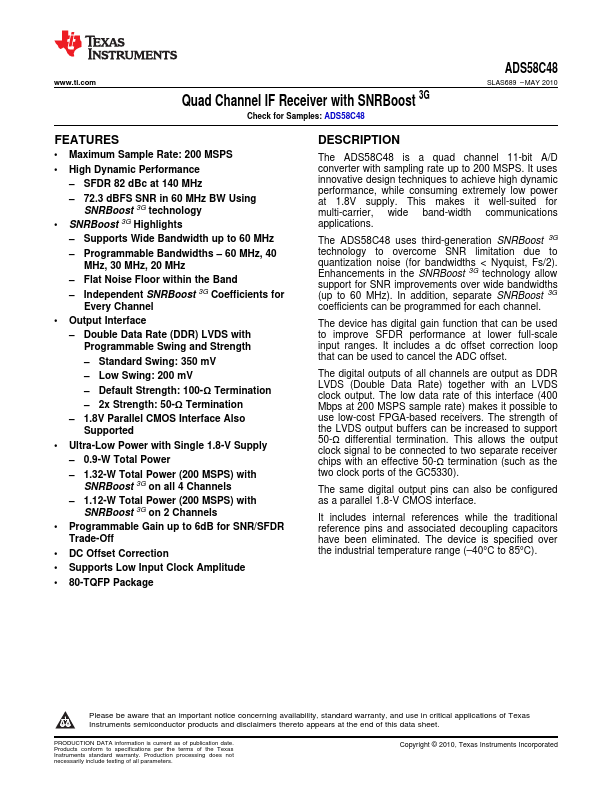

ADS58C48

Description

The ADS58C48 is a quad channel 11-bit A/D converter with sampling rate up to 200 MSPS. It uses innovative design techniques to achieve high dynamic performance, while consuming extremely low power at 1.8V supply.

Key Features

- Maximum Sample Rate: 200 MSPS

- High Dynamic Performance – SFDR 82 dBc at 140 MHz – 72.3 dBFS SNR in 60 MHz BW Using SNRBoost 3G technology

- Programmable Gain up to 6dB for SNR/SFDR Trade-Off

- DC Offset Correction

- Supports Low Input Clock Amplitude

- 80-TQFP Package