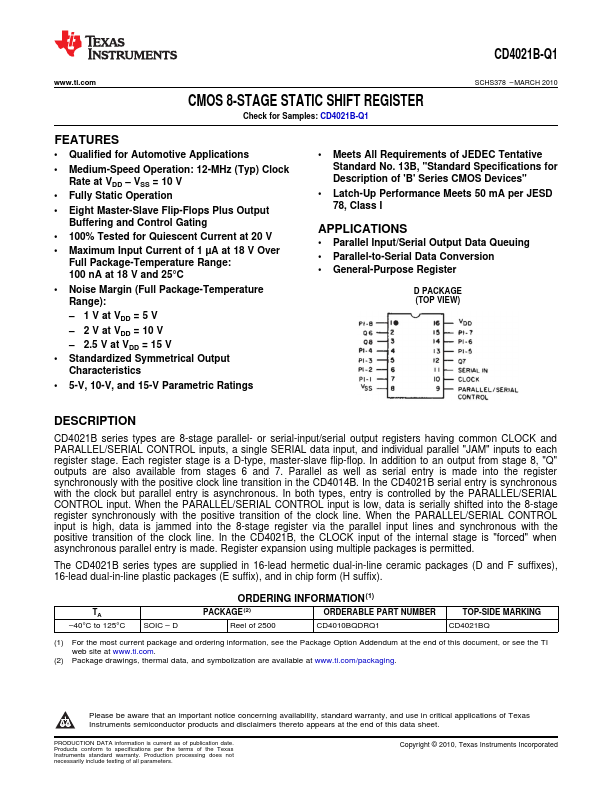

CD4021B-Q1

CD4021B-Q1 is CMOS 8-Stage Static Shift Register manufactured by Texas Instruments.

.ti.

CMOS 8-STAGE STATIC SHIFT REGISTER

Check for Samples: CD4021B-Q1

SCHS378

- MARCH 2010

Features

- Qualified for Automotive Applications

- Medium-Speed Operation: 12-MHz (Typ) Clock

Rate at VDD

- VSS = 10 V

- Fully Static Operation

- Eight Master-Slave Flip-Flops Plus Output

Buffering and Control Gating

- 100% Tested for Quiescent Current at 20 V

- Maximum Input Current of 1 µA at 18 V Over

Full Package-Temperature Range: 100 nA at 18 V and 25°C

- Noise Margin (Full Package-Temperature Range):

- 1 V at VDD = 5 V

- 2 V at VDD = 10 V

- 2.5 V at VDD = 15 V

- Standardized Symmetrical Output Characteristics

- 5-V, 10-V, and 15-V Parametric Ratings

- Meets All...