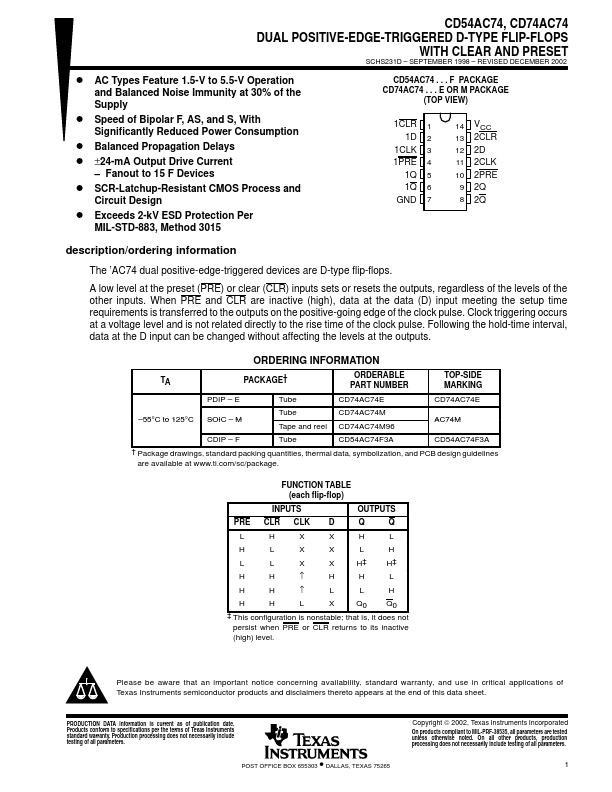

- Part: CD54AC74

- Description: DUAL POSITIVE-EDGE-TRIGGERED D-TYPE FLIP-FLOPS

- Manufacturer: Texas Instruments

- Size: 599.09 KB

Related Texas Instruments Datasheets

| Part Number | Description |

|---|---|

| CD54AC00 | QUADRUPLE 2-INPUT POSITIVE-NAND GATES |

| CD54AC02 | QUADRUPLE 2-INPUT POSITIVE-NOR GATES |

| CD54AC04 | Hex Inverters |

| CD54AC05 | HEX INVERTERS |

| CD54AC08 | QUADRUPLE 2-INPUT POSITIVE-AND GATES |