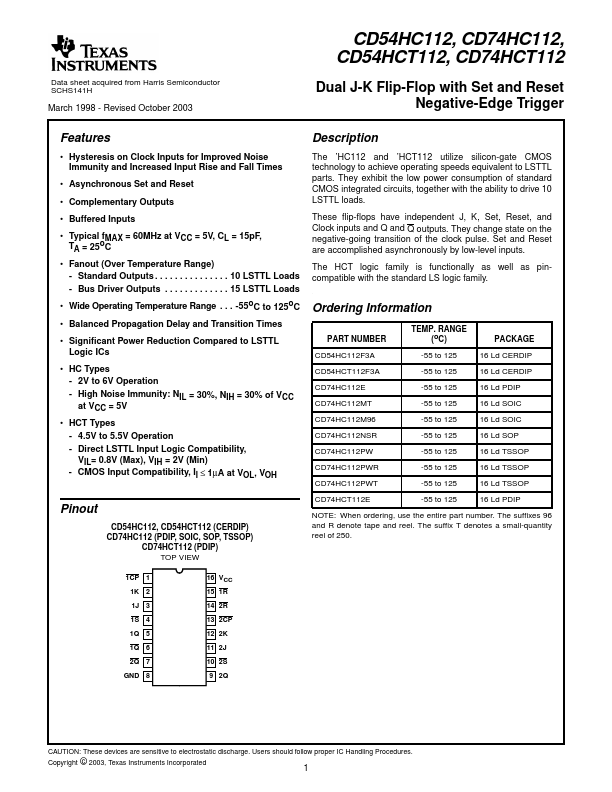

CD54HCT112

Description

Hysteresis on Clock Inputs for Improved Noise Immunity and Increased Input Rise and Fall Times - Asynchronous Set and Reset - plementary Outputs - Buffered Inputs - TTAyp=ic2a5lofCMAX = 60MHz at VCC = 5V, CL = 15pF, - Fanout (Over Temperature Range) - Standard Outputs.