CD74HCT20M

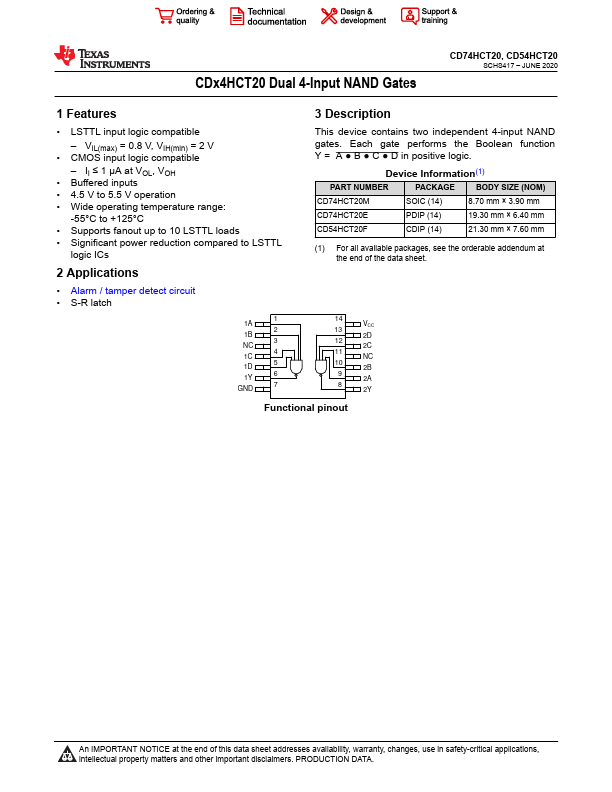

Description

LSTTL input logic compatible - VIL(max) = 0.8 V, VIH(min) = 2 V CMOS input logic compatible - II ≤ 1 µA at VOL, VOH Buffered inputs 4.5 V to 5.5 V operation Wide operating temperature range: -55°C to +125°C Supports fanout up to 10 LSTTL loads Significant power reduction compared to LSTTL logic ICs.