CY74FCT16501T Overview

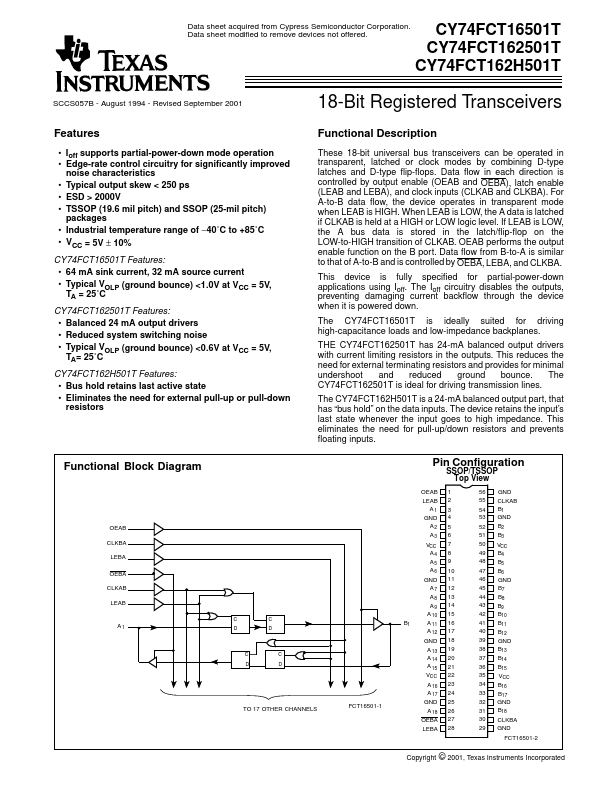

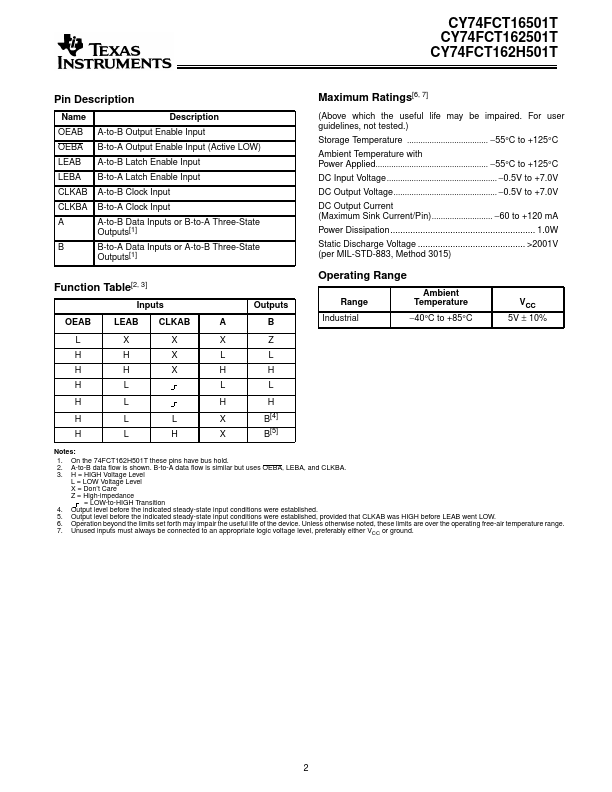

These 18-bit universal bus transceivers can be operated in transparent, latched or clock modes by bining D-type latches and D-type flip-flops. Data flow in each direction is controlled by output enable (OEAB and OEBA), latch enable (LEAB and LEBA), and clock inputs (CLKAB and CLKBA). For A-to-B data flow, the device operates in transparent mode when LEAB is HIGH.

CY74FCT16501T Key Features

- Ioff supports partial-power-down mode operation

- Edge-rate control circuitry for significantly improved

- Typical output skew < 250 ps

- ESD > 2000V

- TSSOP (19.6 mil pitch) and SSOP (25-mil pitch)

- Industrial temperature range of -40˚C to +85˚C

- VCC = 5V ± 10%

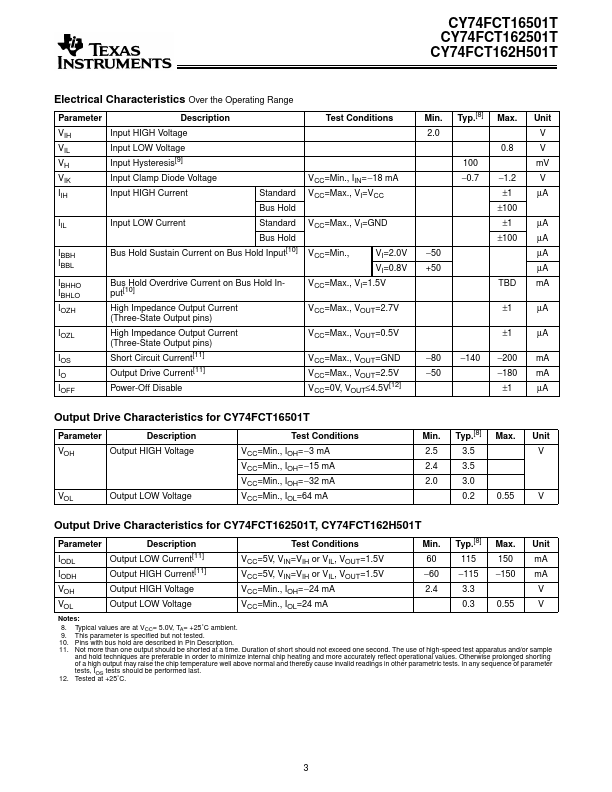

- 64 mA sink current, 32 mA source current

- Typical VOLP (ground bounce) <1.0V at VCC = 5V

- Balanced 24 mA output drivers