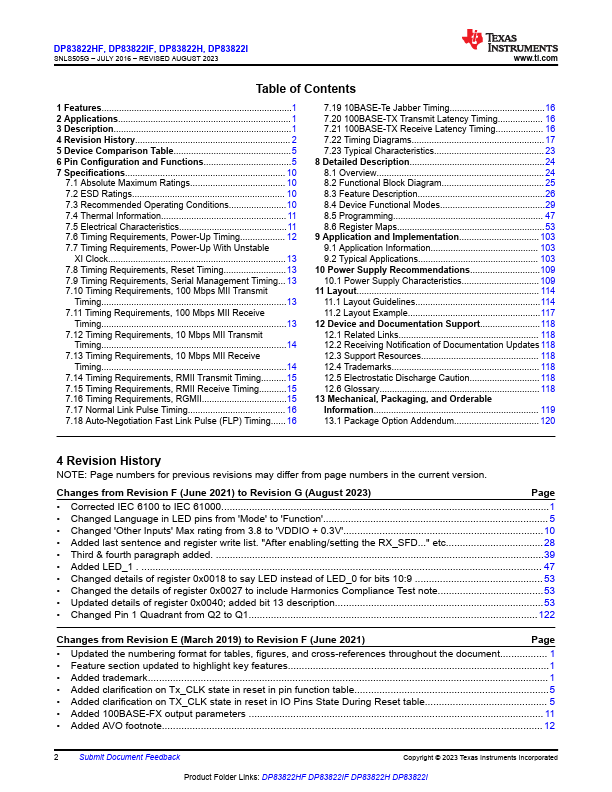

DP83822HF Key Features

- Ultra-robust 10/100Mbs PHY

- IEC 61000-4-2 ESD: +/- 8KV contact discharge

- IEC 61000-4-4 EFT: Class A at 4KV

- CISPR 22 conducted emissions: Class B

- CISPR 22 radiated emissions: Class B

- Operating temperature: -40C to 125C

- MAC interfaces: RGMII / RMII / MII

- IEEE 802.3u pliant: 100BASE-FX, 100BASE

- Flexible supply options

- Low power single supply options