DS110DF1610 Overview

Description

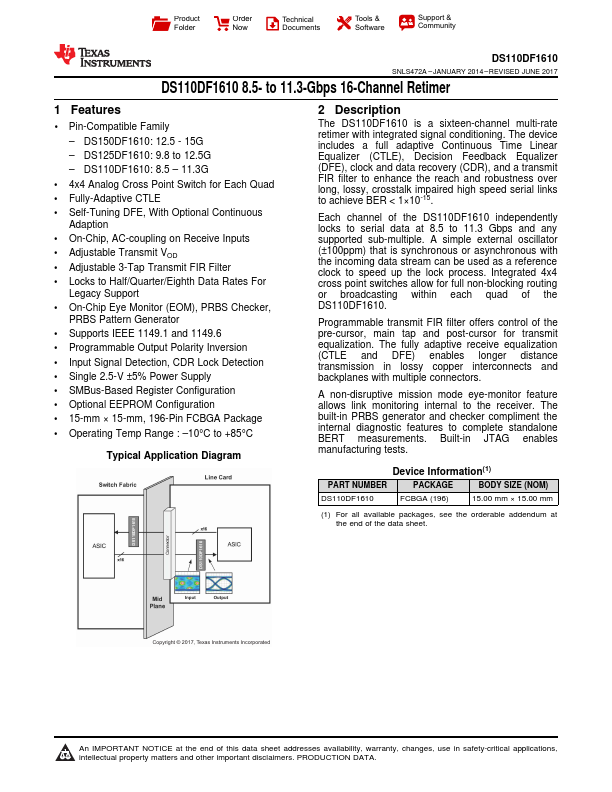

The DS110DF1610 is a sixteen-channel multi-rate retimer with integrated signal conditioning. The device includes a full adaptive Continuous Time Linear Equalizer (CTLE), Decision Feedback Equalizer (DFE), clock and data recovery (CDR), and a transmit FIR filter to enhance the reach and robustness over long, lossy, crosstalk impaired high speed serial links to achieve BER < 1×10-15.

Key Features

- 4x4 Analog Cross Point Switch for Each Quad

- Fully-Adaptive CTLE

- Self-Tuning DFE, With Optional Continuous Adaption

- On-Chip, AC-coupling on Receive Inputs

- Adjustable Transmit VOD

- Adjustable 3-Tap Transmit FIR Filter

- Locks to Half/Quarter/Eighth Data Rates For Legacy Support

- On-Chip Eye Monitor (EOM), PRBS Checker, PRBS Pattern Generator

- Supports IEEE 1149.1 and 1149.6

- Programmable Output Polarity Inversion