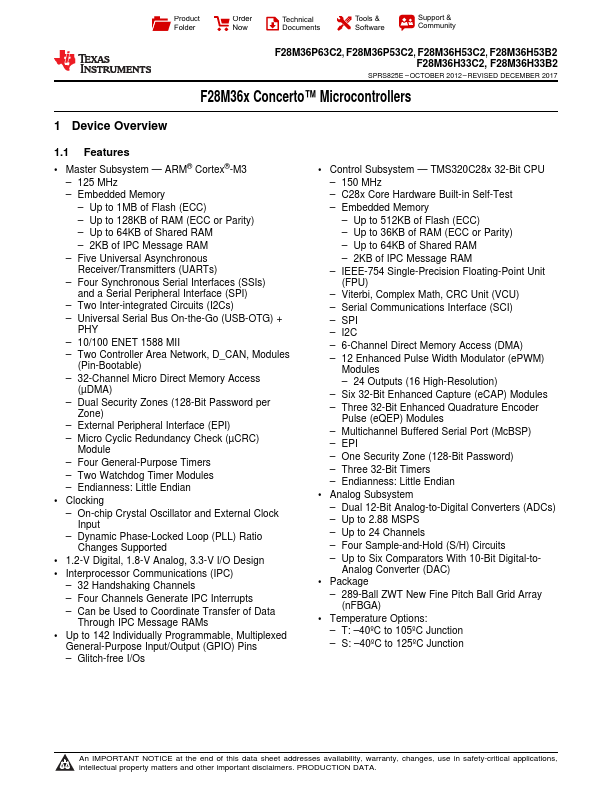

F28M36P53C2 Overview

Key Features

- Master Subsystem

- Clocking – On-chip Crystal Oscillator and External Clock Input – Dynamic Phase-Locked Loop (PLL) Ratio Changes Supported

- 1.2-V Digital, 1.8-V Analog, 3.3-V I/O Design

- Up to 142 Individually Programmable, Multiplexed General-Purpose Input/Output (GPIO) Pins – Glitch-free I/Os

- Control Subsystem