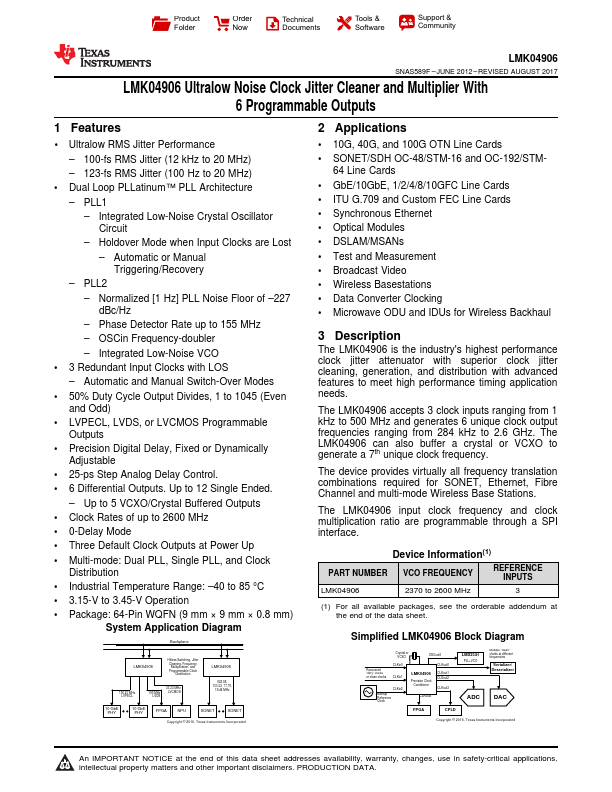

LMK04906

Overview

- 1 Ultralow RMS Jitter Performance - 100-fs RMS Jitter (12 kHz to 20 MHz) - 123-fs RMS Jitter (100 Hz to 20 MHz)

- Dual Loop PLLatinum™ PLL Architecture - PLL1 - Integrated Low-Noise Crystal Oscillator Circuit - Holdover Mode when Input Clocks are Lost - Automatic or Manual Triggering/Recovery - PLL2 - Normalized [1 Hz] PLL Noise Floor of -227 dBc/Hz - Phase Detector Rate up to 155 MHz - OSCin Frequency-doubler - Integrated Low-Noise VCO

- 3 Redundant Input Clocks with LOS - Automatic and Manual Switch-Over Modes

- 50% Duty Cycle Output Divides, 1 to 1045 (Even and Odd)

- LVPECL, LVDS, or LVCMOS Programmable Outputs

- Precision Digital Delay, Fixed or Dynamically Adjustable

- 25-ps Step Analog Delay Control.

- 6 Differential Outputs. Up to 12 Single Ended. - Up to 5 VCXO/Crystal Buffered Outputs

- Clock Rates of up to 2600 MHz

- 0-Delay Mode