LMK5B12204

Overview

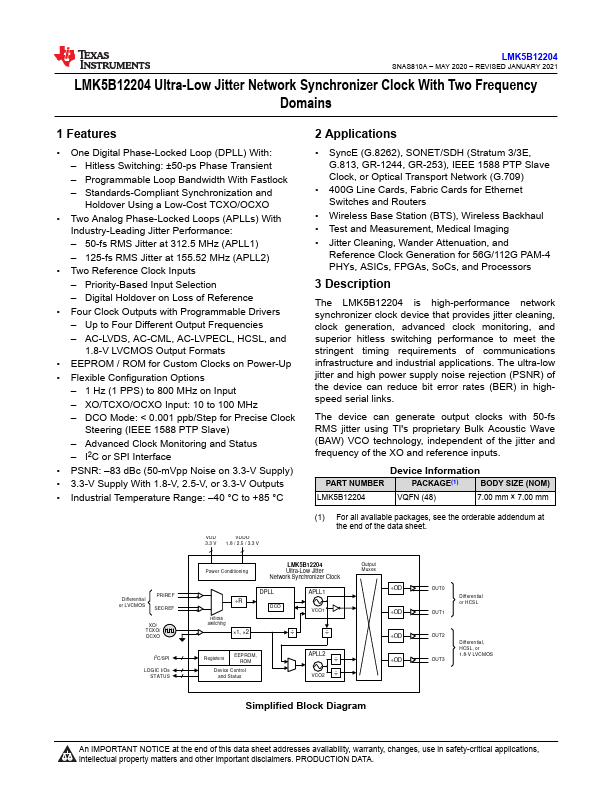

The LMK5B12204 is high-performance network synchronizer clock device that provides jitter cleaning, clock generation, advanced clock monitoring, and superior hi.

- One Digital Phase-Locked Loop (DPLL) With: - Hitless Switching: ±50-ps Phase Transient - Programmable Loop Bandwidth With Fastlock - Standards-Compliant Synchronization and Holdover Using a Low-Cost TCXO/OCXO

- Two Analog Phase-Locked Loops (APLLs) With Industry-Leading Jitter Performance: - 50-fs RMS Jitter at 312.5 MHz (APLL1) - 125-fs RMS Jitter at 155.52 MHz (APLL2)

- Two Reference Clock Inputs - Priority-Based Input Selection - Digital Holdover on Loss of Reference

- Four Clock Outputs with Programmable Drivers - Up to Four Different Output Frequencies - AC-LVDS, AC-CML, AC-LVPECL, HCSL, and 1.8-V LVCMOS Output Formats

- EEPROM / ROM for Custom Clocks on Power-Up

- Flexible Configuration Options - 1 Hz (1 PPS) to 800 MHz on Input - XO/TCXO/OCXO Input: 10 to 100 MHz - DCO Mode: < 0.001 ppb/Step for Precise Clock Steering (IEEE 1588 PTP Slave) - Advanced Clock Monitoring and Status - I2C or SPI Interface

- PSNR: -83 dBc (50-mVpp Noise on 3.3-V Supply)

- 3.3-V Supply With 1.8-V, 2.5-V, or 3.3-V Outputs

- Industrial Temperature Range: -40 °C to +85 °C VDD 3.3 V VDDO 1.8 / 2.5 / 3.3 V