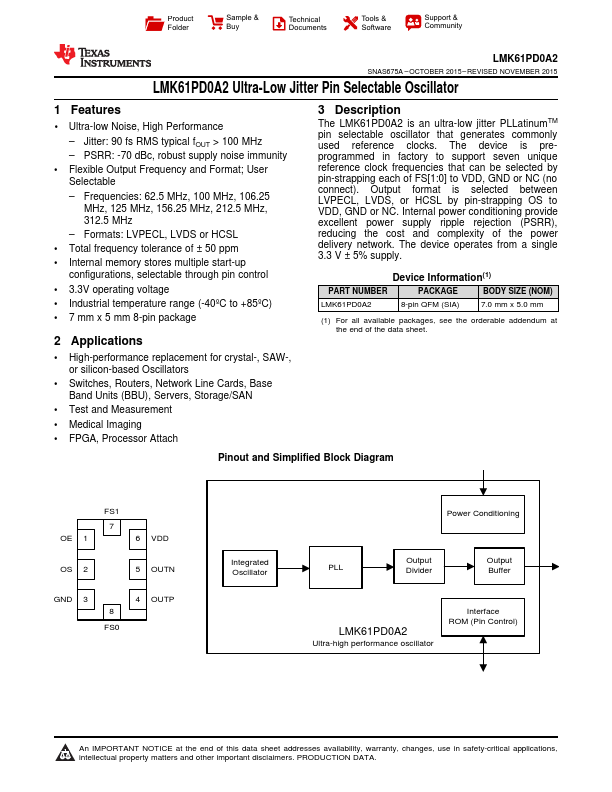

LMK61PD0A2 Key Features

- 1 Ultra-low Noise, High Performance

- Jitter: 90 fs RMS typical fOUT > 100 MHz

- PSRR: -70 dBc, robust supply noise immunity

- Flexible Output Frequency and Format; User Selectable

- Formats: LVPECL, LVDS or HCSL

- Total frequency tolerance of ± 50 ppm

- Internal memory stores multiple start-up

- 3.3V operating voltage

- Industrial temperature range (-40ºC to +85ºC)

- 7 mm x 5 mm 8-pin package