RM48L730

Description

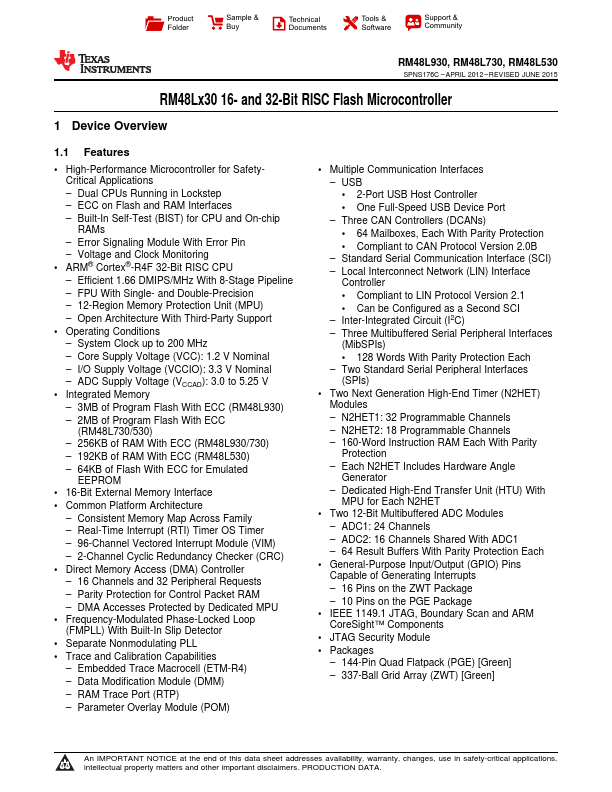

The RM48Lx30 device is a high-performance microcontroller family for safety systems. The safety architecture includes dual CPUs in lockstep, CPU and memory BIST logic, ECC on both the flash and the data SRAM, parity on peripheral memories, and loopback capability on peripheral I/Os.

Key Features

- High-Performance Microcontroller for SafetyCritical Applications - Dual CPUs Running in Lockstep - ECC on Flash and RAM Interfaces - Built-In Self-Test (BIST) for CPU and On-chip RAMs - Error Signaling Module With Error Pin - Voltage and Clock Monitoring

- ARM® Cortex®-R4F 32-Bit RISC CPU - Efficient 1.66 DMIPS/MHz With 8-Stage Pipeline - FPU With Single- and Double-Precision - 12-Region Memory Protection Unit (MPU) - Open Architecture With Third-Party Support

- Operating Conditions - System Clock up to 200 MHz - Core Supply Voltage (VCC): 1.2 V Nominal - I/O Supply Voltage (VCCIO): 3.3 V Nominal - ADC Supply Voltage (VCCAD): 3.0 to 5.25 V

- Integrated Memory - 3MB of Program Flash With ECC (RM48L930) - 2MB of Program Flash With ECC (RM48L730/530) - 256KB of RAM With ECC (RM48L930/730) - 192KB of RAM With ECC (RM48L530) - 64KB of Flash With ECC for Emulated EEPROM

- 16-Bit External Memory Interface

- Common Platform Architecture - Consistent Memory Map Across Family - Real-Time Interrupt (RTI) Timer OS Timer - 96-Channel Vectored Interrupt Module (VIM) - 2-Channel Cyclic Redundancy Checker (CRC)

- Direct Memory Access (DMA) Controller - 16 Channels and 32 Peripheral Requests - Parity Protection for Control Packet RAM - DMA Accesses Protected by Dedicated MPU

- Frequency-Modulated Phase-Locked Loop (FMPLL) With Built-In Slip Detector

- Separate Nonmodulating PLL

- Trace and Calibration Capabilities - Embedded Trace Macrocell (ETM-R4) - Data Modification Module (DMM) - RAM Trace Port (RTP) - Parameter Overlay Module (POM)