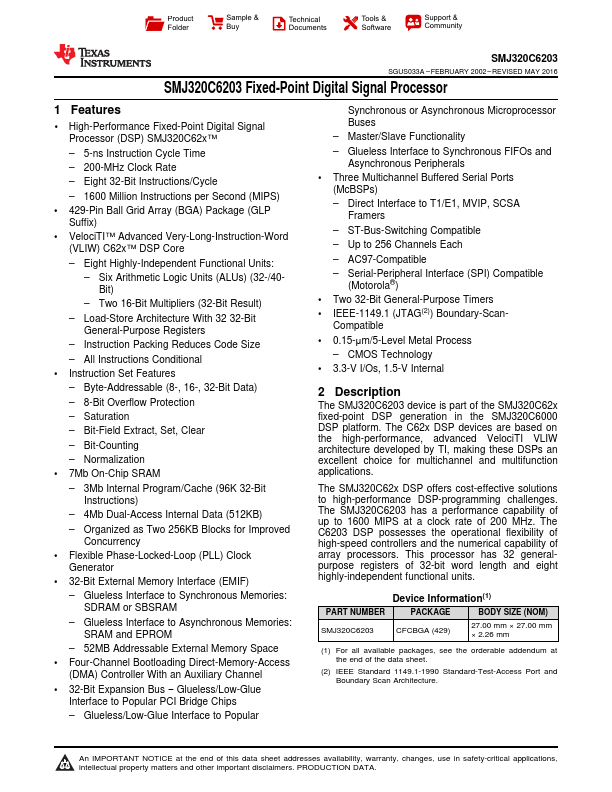

SMJ320C6203

SMJ320C6203 is Digital Signal Processor manufactured by Texas Instruments.

Features

- 1 High-Performance Fixed-Point Digital Signal Processor (DSP) SMJ320C62x™

- 5-ns Instruction Cycle Time

- 200-MHz Clock Rate

- Eight 32-Bit Instructions/Cycle

- 1600 Million Instructions per Second (MIPS)

- 429-Pin Ball Grid Array (BGA) Package (GLP Suffix)

- Veloci TI™ Advanced Very-Long-Instruction-Word (VLIW) C62x™ DSP Core

- Eight Highly-Independent Functional Units:

- Six Arithmetic Logic Units (ALUs) (32-/40Bit)

- Two 16-Bit Multipliers (32-Bit Result)

- Load-Store Architecture With 32 32-Bit General-Purpose Registers

- Instruction Packing Reduces Code Size

- All Instructions Conditional

- Instruction Set Features

- Byte-Addressable (8-, 16-, 32-Bit Data)

- 8-Bit Overflow Protection

- Saturation

- Bit-Field Extract, Set, Clear

- Bit-Counting

- Normalization

- 7Mb On-Chip SRAM

- 3Mb Internal Program/Cache (96K 32-Bit Instructions)

- 4Mb Dual-Access Internal Data (512KB)

- Organized as Two 256KB Blocks for Improved Concurrency

- Flexible Phase-Locked-Loop (PLL) Clock Generator

- 32-Bit External Memory Interface (EMIF)

- Glueless Interface to Synchronous Memories: SDRAM or SBSRAM

- Glueless Interface to Asynchronous Memories: SRAM and EPROM

- 52MB Addressable External Memory Space

- Four-Channel Bootloading Direct-Memory-Access (DMA) Controller With an Auxiliary Channel

- 32-Bit Expansion Bus

- Glueless/Low-Glue Interface to Popular PCI Bridge Chips

- Glueless/Low-Glue Interface to Popular

Synchronous or Asynchronous Microprocessor Buses

- Master/Slave Functionality

- Glueless Interface to Synchronous FIFOs and Asynchronous Peripherals

- Three Multichannel Buffered Serial Ports (Mc BSPs)

- Direct Interface to T1/E1, MVIP, SCSA Framers

- ST-Bus-Switching...